- 1

- 2

- 3

- 4

- 5

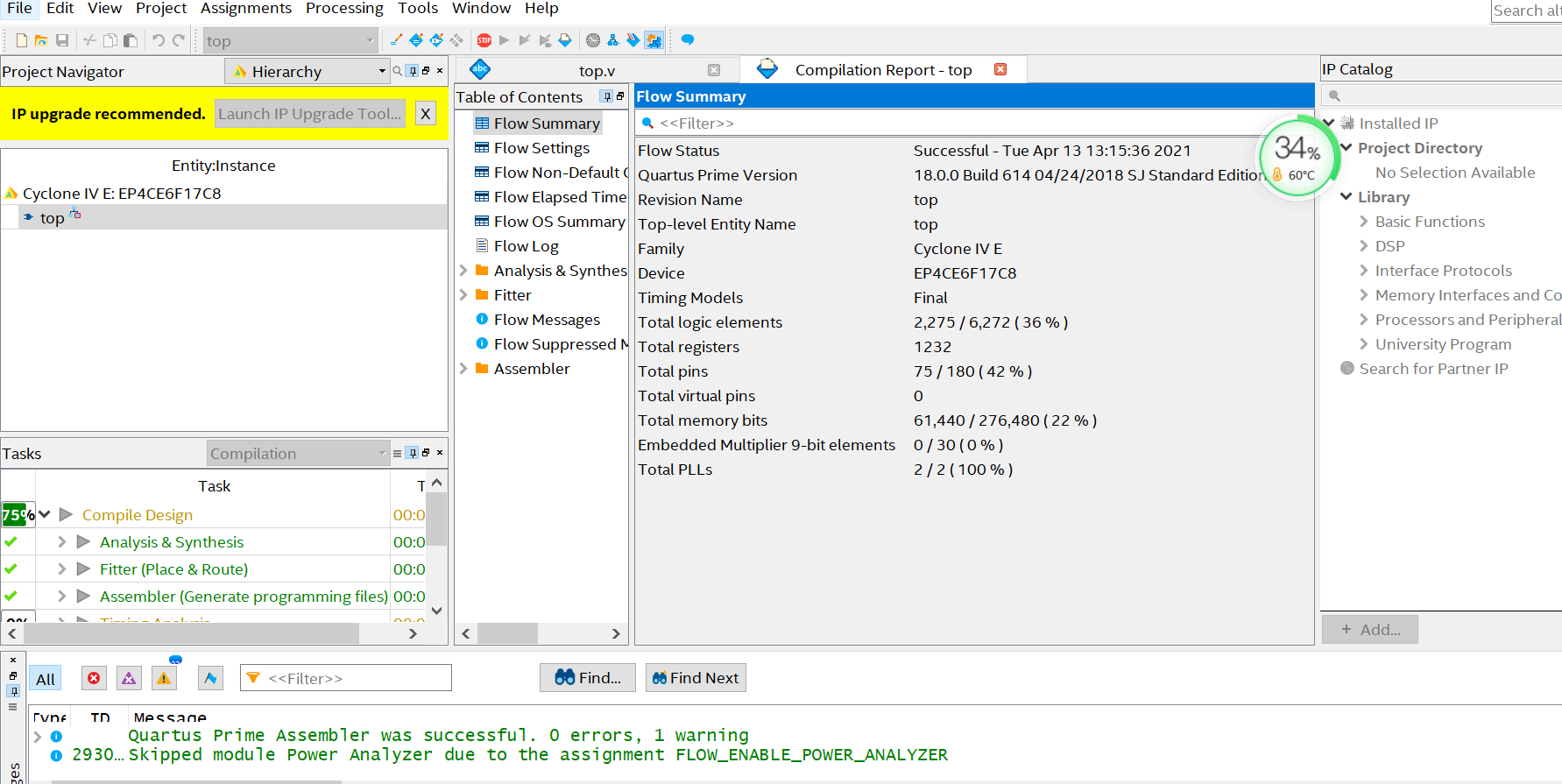

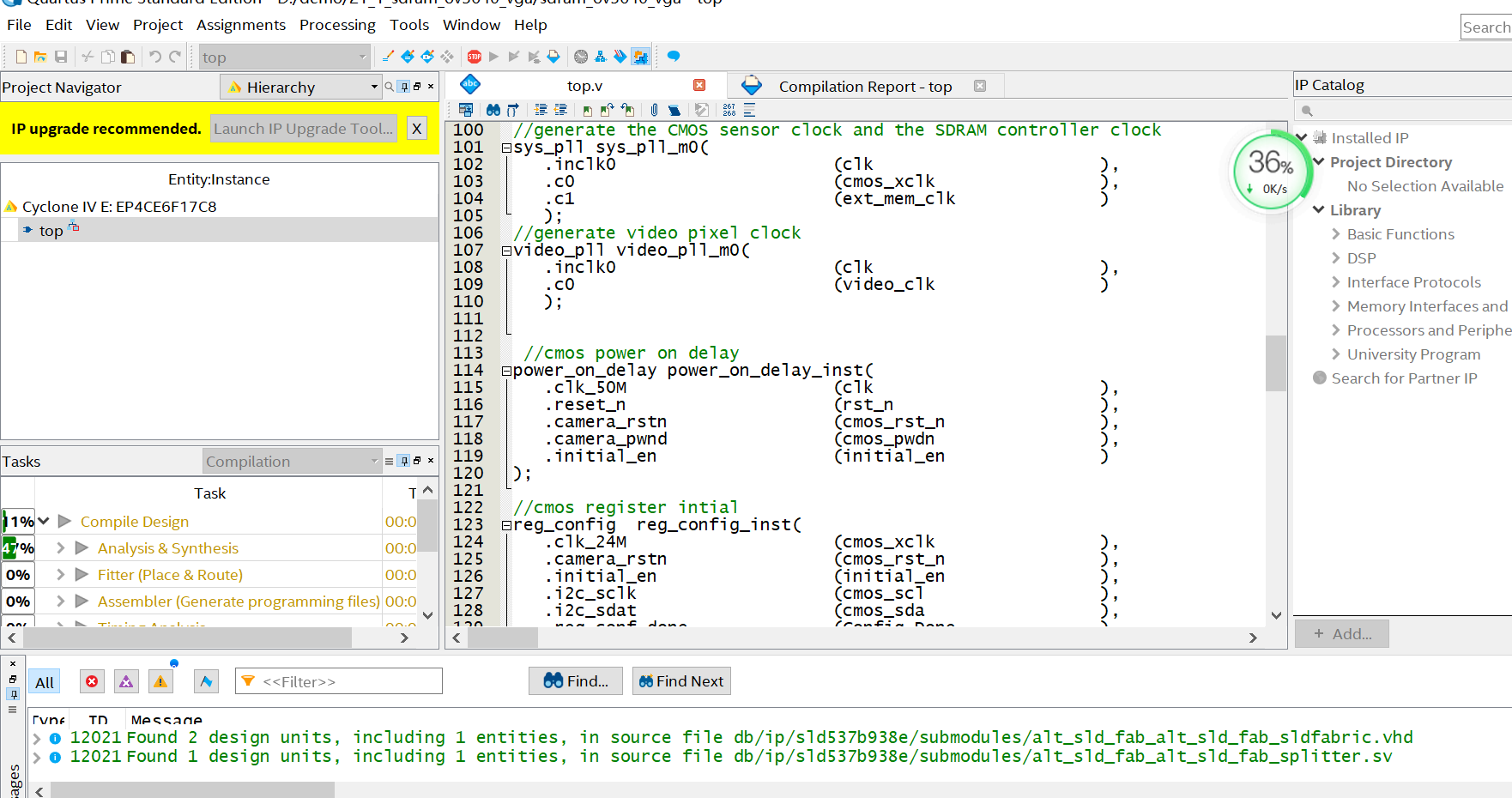

FPGA读取OV5640摄像头数据并通过VGA或LCD屏显示输出的Verilog逻辑源码Quartu

资料介绍

FPGA读取OV5640摄像头数据并通过VGA或LCD屏显示输出的Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

module top(

input clk,

input rst_n,

output cmos_scl, //cmos i2c clock

inout cmos_sda, //cmos i2c data

input cmos_vsync, //cmos vsync

input cmos_href, //cmos hsync refrence,data valid

input cmos_pclk, //cmos pxiel clock

output cmos_xclk, //cmos externl clock

input [7:0] cmos_db, //cmos data

output cmos_rst_n, //cmos reset

output cmos_pwdn, //cmos power down

output vga_out_hs, //vga horizontal synchronization

output vga_out_vs, //vga vertical synchronization

output[4:0] vga_out_r, //vga red

output[5:0] vga_out_g, //vga green

output[4:0] vga_out_b, //vga blue

output sdram_clk, //sdram clock

output sdram_cke, //sdram clock enable

output sdram_cs_n, //sdram chip select

output sdram_we_n, //sdram write enable

output sdram_cas_n, //sdram column address strobe

output sdram_ras_n, //sdram row address strobe

output[1:0] sdram_dqm, //sdram data enable

output[1:0] sdram_ba, //sdram bank address

output[12:0] sdram_addr, //sdram address

inout[15:0] sdram_dq //sdram data

);

部分文件列表

| 文件名 | 大小 |

| 21.OV5640摄像头显示例程.pdf | |

| 21_1_sdram_ov5640_vga/ | |

| 21_1_sdram_ov5640_vga/ax301_ax4010_base.tcl | 1KB |

| 21_1_sdram_ov5640_vga/db/ | |

| 21_1_sdram_ov5640_vga/db/.cmp.kpt | |

| 21_1_sdram_ov5640_vga/db/.ipregen.qmsg | 2KB |

| 21_1_sdram_ov5640_vga/db/a_gray2bin_6ib.tdf | 2KB |

| 21_1_sdram_ov5640_vga/db/a_graycounter_1lc.tdf | 4KB |

| 21_1_sdram_ov5640_vga/db/a_graycounter_577.tdf | 4KB |

| 21_1_sdram_ov5640_vga/db/alt_synch_pipe_8pl.tdf | 3KB |

| 21_1_sdram_ov5640_vga/db/alt_synch_pipe_9pl.tdf | 3KB |

| ... | |

最新上传

-

21ic小能手 打赏10.00元 11小时前

-

21ic小能手 打赏10.00元 11小时前

-

21ic小能手 打赏5.00元 11小时前

资料:STM32智能交流电检测

-

21ic小能手 打赏5.00元 11小时前

-

21ic小能手 打赏5.00元 11小时前

-

21ic小能手 打赏10.00元 11小时前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏15.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:gsy幸运

-

21ic下载 打赏310.00元 3天前

用户:小猫做电路

-

21ic下载 打赏360.00元 3天前

用户:mulanhk

-

21ic下载 打赏230.00元 3天前

用户:江岚

-

21ic下载 打赏230.00元 3天前

用户:潇潇江南

-

21ic下载 打赏210.00元 3天前

用户:zhengdai

-

21ic下载 打赏160.00元 3天前

用户:lanmukk

-

21ic下载 打赏130.00元 3天前

用户:jh03551

-

21ic下载 打赏110.00元 3天前

用户:liqiang9090

-

21ic下载 打赏110.00元 3天前

用户:jh0355

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏20.00元 3天前

用户:w178191520

-

21ic下载 打赏30.00元 3天前

用户:sun2152

全部评论(0)