- 1

- 2

- 3

- 4

- 5

FPGA控制VGA接口显示屏8种色彩的循环变化实验Verilog逻辑源码Quartus11.0工程文

资料介绍

FPGA控制VGA接口显示屏8种色彩的循环变化实验Verilog逻辑源码Quartus11.0工程文件, FPGA型号为CYCLONE4E系列中的EP4CE6E22C8,可以做为你的学习设计参考。

module VGA(clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b,coldata);

input clk; //系统时钟50MHz

input rst_n; //低电平复位

input[8:0] coldata; //需要显示的色彩,使用者可以自己在color.v中改变数值以获取需要的色彩,该例程实现的是8种色彩的循环变化

output hsync; //行同步信号

output vsync; //场同步信号

output[2:0] vga_r; //红基色信号

output[2:0] vga_g; //绿基色信号

output[2:0] vga_b; //蓝基色信号

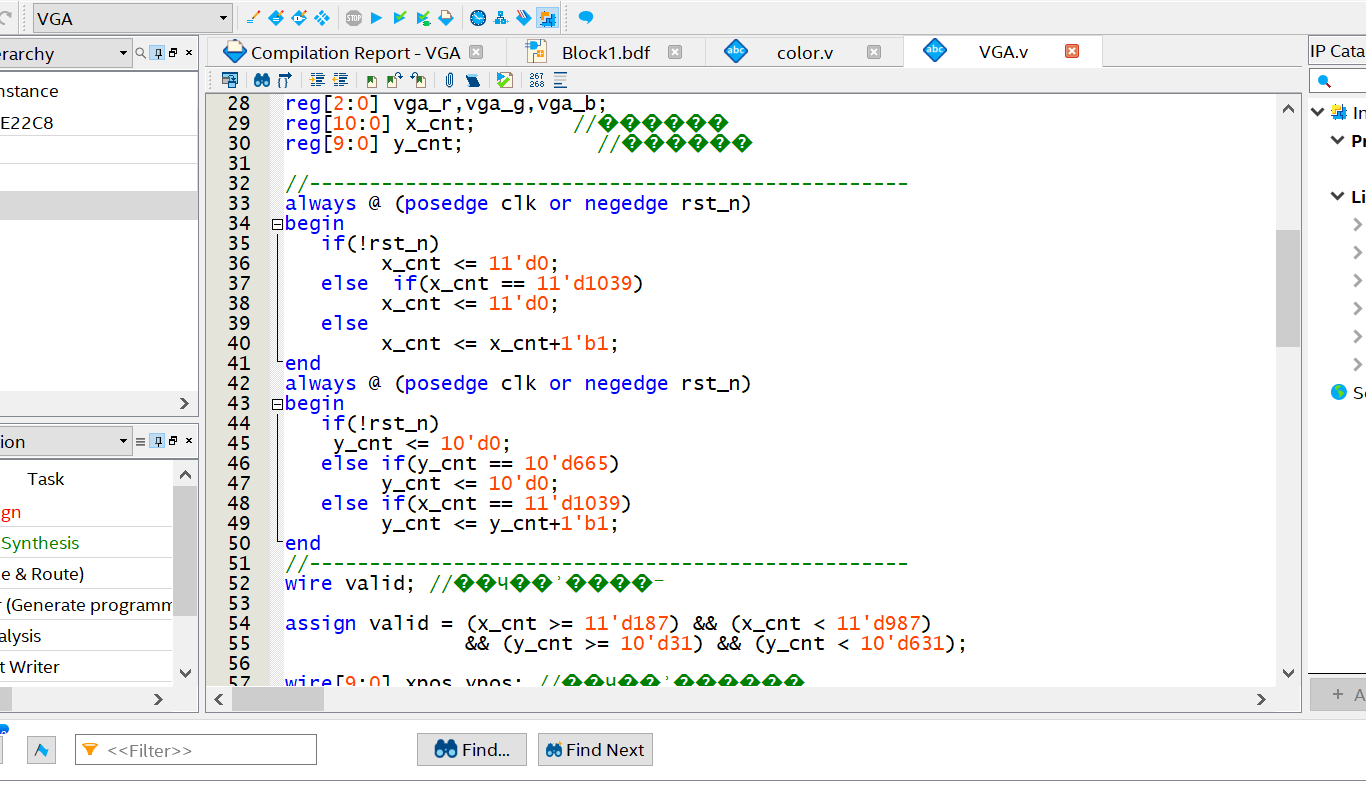

reg[2:0] vga_r,vga_g,vga_b;

reg[10:0] x_cnt; //行坐标

reg[9:0] y_cnt; //列坐标

//--------------------------------------------------

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

x_cnt <= 11'd0;

else if(x_cnt == 11'd1039)

x_cnt <= 11'd0;

else

x_cnt <= x_cnt+1'b1;

end

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

y_cnt <= 10'd0;

else if(y_cnt == 10'd665)

y_cnt <= 10'd0;

else if(x_cnt == 11'd1039)

y_cnt <= y_cnt+1'b1;

end

//--------------------------------------------------

wire valid; //有效显示区标志

assign valid = (x_cnt >= 11'd187) && (x_cnt < 11'd987)

&& (y_cnt >= 10'd31) && (y_cnt < 10'd631);

wire[9:0] xpos,ypos; //有效显示区坐标

assign xpos = x_cnt-11'd187;

assign ypos = y_cnt-10'd31;

//--------------------------------------------------

reg hsync_r,vsync_r; //同步信号产生

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n) hsync_r <= 1'b1;

else if(x_cnt == 11'd0) hsync_r <= 1'b0; //产生hsync信号

else if(x_cnt == 11'd120) hsync_r <= 1'b1;

end

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n) vsync_r <= 1'b1;

else if(y_cnt == 10'd0) vsync_r <= 1'b0; //产生vsync信号

else if(y_cnt == 10'd6) vsync_r <= 1'b1;

end

assign hsync = hsync_r;

assign vsync = vsync_r;

//--------------------------------------------------

wire dis; //显示屏显示范围

assign dis = ( (xpos>=80) && (xpos<=720) )

&& ( (ypos>=60) && (ypos<=540) );

//--------------------------------------------------

//分别对RGB的3位数据进行判断

//R,G,B控制液晶屏颜色显示

//最终显示屏显示的颜色是RGB3种颜色的叠加

部分文件列表

| 文件名 | 大小 |

| lab4_VGA/ | |

| lab4_VGA/Block1.bdf | 7KB |

| lab4_VGA/VGA.asm.rpt | 8KB |

| lab4_VGA/VGA.bsf | 3KB |

| lab4_VGA/VGA.cdf | |

| lab4_VGA/VGA.done | |

| lab4_VGA/VGA.fit.rpt | |

| lab4_VGA/VGA.fit.smsg | 1KB |

| lab4_VGA/VGA.fit.summary | 1KB |

| lab4_VGA/VGA.flow.rpt | 9KB |

| lab4_VGA/VGA.map.rpt | |

| ... | |

最新上传

-

21ic小能手 打赏5.00元 3天前

-

21下载积分 打赏1.00元 3天前

用户:德才兼备

-

mulanhk 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:数控电子负载-CH552

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:zhengdai

-

21ic下载 打赏310.00元 3天前

用户:liqiang9090

-

21ic下载 打赏330.00元 3天前

用户:jh0355

-

21ic下载 打赏210.00元 3天前

用户:小猫做电路

-

21ic下载 打赏240.00元 3天前

用户:jh03551

-

21ic下载 打赏210.00元 3天前

用户:gsy幸运

-

21ic下载 打赏70.00元 3天前

用户:w178191520

-

21ic下载 打赏60.00元 3天前

用户:sun2152

-

21ic下载 打赏80.00元 3天前

用户:江岚

-

21ic下载 打赏60.00元 3天前

用户:xuzhen1

-

21ic下载 打赏20.00元 3天前

用户:kk1957135547

-

21ic下载 打赏40.00元 3天前

用户:潇潇江南

-

21ic下载 打赏20.00元 3天前

用户:w993263495

-

21ic下载 打赏20.00元 3天前

用户:w1966891335

-

21ic下载 打赏70.00元 3天前

用户:有理想666

-

21ic下载 打赏35.00元 3天前

用户:xzxbybd

-

21ic下载 打赏15.00元 3天前

用户:x15580286248

-

21ic下载 打赏25.00元 3天前

用户:铁蛋锅

-

21ic下载 打赏35.00元 3天前

用户:mulanhk

全部评论(0)