- 1

- 2

- 3

- 4

- 5

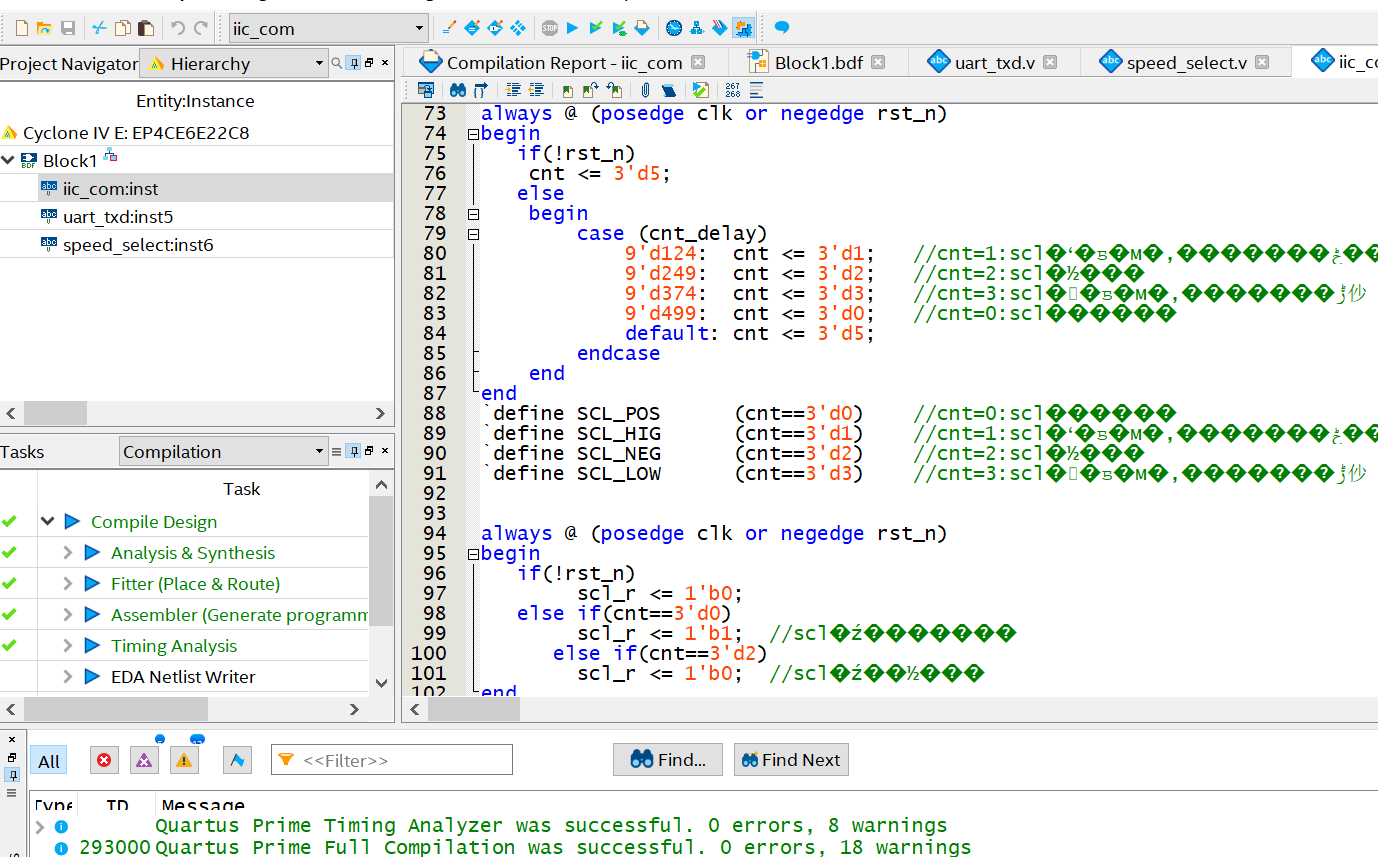

FPGA读写EEPROM芯片AT24C02实验Verilog逻辑源码Quartus11.0工程文件

资料介绍

FPGA读写EEPROM芯片AT24C02实验Verilog逻辑源码Quartus11.0工程文件, FPGA型号为CYCLONE4E系列中的EP4CE6E22C8,可以做为你的学习设计参考。

module iic_com(

clk,rst_n,

sw1,sw2,

scl,sda,

dis_data

);

input clk; // 50MHz

input rst_n; //复位信号,低有效

input sw1,sw2; //按键1、2,(1按下执行写入操作,2按下执行读操作)

output scl; // 24C02的时钟端口

inout sda; // 24C02的数据端口

output[7:0] dis_data; //数码管显示的数据

//按键检测

reg sw1_r,sw2_r; //键值锁存寄存器,每20ms检测一次键值

reg[19:0] cnt_20ms; //20ms计数寄存器

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_20ms <= 20'd0;

else

cnt_20ms <= cnt_20ms+1'b1; //不断计数

end

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

sw1_r <= 1'b1; //键值寄存器复位,没有键盘按下时键值都为1

sw2_r <= 1'b1;

end

else if(cnt_20ms == 20'hfffff)

begin

sw1_r <= sw1; //按键1值锁存

sw2_r <= sw2; //按键2值锁存

end

end

//---------------------------------------------

//分频部分

reg[2:0] cnt; // cnt=0:scl上升沿,cnt=1:scl高电平中间,cnt=2:scl下降沿,cnt=3:scl低电平中间

reg[8:0] cnt_delay; //500循环计数,产生iic所需要的时钟

reg scl_r; //时钟脉冲寄存器

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_delay <= 9'd0;

else if(cnt_delay == 9'd499)

cnt_delay <= 9'd0; //计数到10us为scl的周期,即100KHz

else

cnt_delay <= cnt_delay+1'b1; //时钟计数

end

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 3'd5;

else

begin

case (cnt_delay)

9'd124: cnt <= 3'd1; //cnt=1:scl高电平中间,用于数据采样

9'd249: cnt <= 3'd2; //cnt=2:scl下降沿

9'd374: cnt <= 3'd3; //cnt=3:scl低电平中间,用于数据变化

9'd499: cnt <= 3'd0; //cnt=0:scl上升沿

default: cnt <= 3'd5;

endcase

end

end

`define SCL_POS (cnt==3'd0) //cnt=0:scl上升沿

`define SCL_HIG (cnt==3'd1) //cnt=1:scl高电平中间,用于数据采样

`define SCL_NEG (cnt==3'd2) //cnt=2:scl下降沿

`define SCL_LOW (cnt==3'd3) //cnt=3:scl低电平中间,用于数据变化

部分文件列表

| 文件名 | 大小 |

| lab3_IIC/ | |

| lab3_IIC/Block1.bdf | |

| lab3_IIC/db/ | |

| lab3_IIC/db/iic_com.(0).cnf.cdb | 2KB |

| lab3_IIC/db/iic_com.(0).cnf.hdb | 1KB |

| lab3_IIC/db/iic_com.(1).cnf.cdb | |

| lab3_IIC/db/iic_com.(1).cnf.hdb | 2KB |

| lab3_IIC/db/iic_com.(2).cnf.cdb | 6KB |

| lab3_IIC/db/iic_com.(2).cnf.hdb | 2KB |

| lab3_IIC/db/iic_com.(3).cnf.cdb | 2KB |

| lab3_IIC/db/iic_com.(3).cnf.hdb | 1KB |

| ... | |

相关下载

- 2025版建设工程消防验收技术图集 高清彩图新...

- JBT4730.6-2005承压设备无损检测第6部分:涡...

- JBT4730.5-2005承压设备无损检测第5部分:渗...

- JBT4730.4-2005承压设备无损检测第4部分:磁...

- JBT4730.3-2005承压设备无损检测第3部分:超...

- JBT4730.2-2005承压设备无损检测第2部分:射...

- JBT4730.1-2005承压设备无损检测第1部分:通...

- HJ652-2013矿山生态环境保护与恢复治理方案(...

- HJ651-2013矿山生态环境保护与恢复治理技术规...

- HJ450-2008清洁生产标准印制电路板制造业

最新上传

-

21ic小能手 打赏5.00元 10小时前

-

21ic小能手 打赏5.00元 2天前

-

21ic小能手 打赏10.00元 2天前

-

21ic小能手 打赏5.00元 2天前

-

21ic小能手 打赏5.00元 2天前

-

21ic小能手 打赏5.00元 2天前

-

21ic小能手 打赏5.00元 3天前

-

21下载积分 打赏1.00元 3天前

用户:德才兼备

-

mulanhk 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:数控电子负载-CH552

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:zhengdai

-

21ic下载 打赏310.00元 3天前

用户:liqiang9090

-

21ic下载 打赏330.00元 3天前

用户:jh0355

-

21ic下载 打赏210.00元 3天前

用户:小猫做电路

-

21ic下载 打赏240.00元 3天前

用户:jh03551

-

21ic下载 打赏210.00元 3天前

用户:gsy幸运

-

21ic下载 打赏70.00元 3天前

用户:w178191520

-

21ic下载 打赏60.00元 3天前

用户:sun2152

-

21ic下载 打赏80.00元 3天前

用户:江岚

-

21ic下载 打赏60.00元 3天前

用户:xuzhen1

-

21ic下载 打赏20.00元 3天前

用户:kk1957135547

-

21ic下载 打赏40.00元 3天前

用户:潇潇江南

-

21ic下载 打赏20.00元 3天前

用户:w993263495

全部评论(1)

2023-12-12 14:28:10mmmhh

666