- 1

- 2

- 3

- 4

- 5

28BYJ-48步进电机(EP4CE6)FPGA控制Verilog逻辑源码Quartus工程文件+文

资料介绍

28BYJ-48步进电机(EP4CE6)FPGA控制Verilog逻辑源码Quartus工程文件+文档资料,

28BYJ-48步进电机:

步进电机是一种将电脉冲转化为角位移的执行机构。通俗一点讲:当步进驱动器接收到一个脉冲信号,它就驱动步进电机按设定的方向转动一个固定的角度(及步进角)。您可以通过控制脉冲个来控制角位移量,从而达到准确定位的目的;同时您可以通过控制脉冲频率来控制电机转动的速度和加速度,从而达到调速的目的。

2. 步进电机规格:

步进电机28BYJ48型四相八拍电机,电压为DC5V—DC12V。

3. 实现原理

当对步进电机施加一系列连续不断的控制脉冲时,它可以连续不断地转动。每一个脉冲信号对应步进电机的某一相或两相绕组的通电状态改变一次,也就对应转子转过一定的角度(一个步距角)。当通电状态的改变完成一个循环时,转子转过一个齿距。四相步进电机可以在不同的通电方式下运行,常见的通电方式有单(单相绕组通电)四拍(A-B-C-D-A。。。),双(双相绕组通电)四拍(AB-BC-CD-DA-AB-。。。),八拍(A-AB-B-BC-C-CD-D-DA-A。。。)

module STEP_MOTO_V1_0 (

//input

input sys_clk ,

input sys_rst_n ,

input [2:0] key ,

output reg mot_out_a ,

output reg mot_out_b ,

output reg mot_out_c ,

output reg mot_out_d

);

//reg define

//reg [8-1:0] counter ;

//reg [8-1:0] count ;

reg [25:0] clk_cnt ;

reg [ 2:0] step_cnt ;

//wire

wire step_en ;

//wire define

//parameter define

/*******************************************************************************************************

** Main Program

**

********************************************************************************************************/

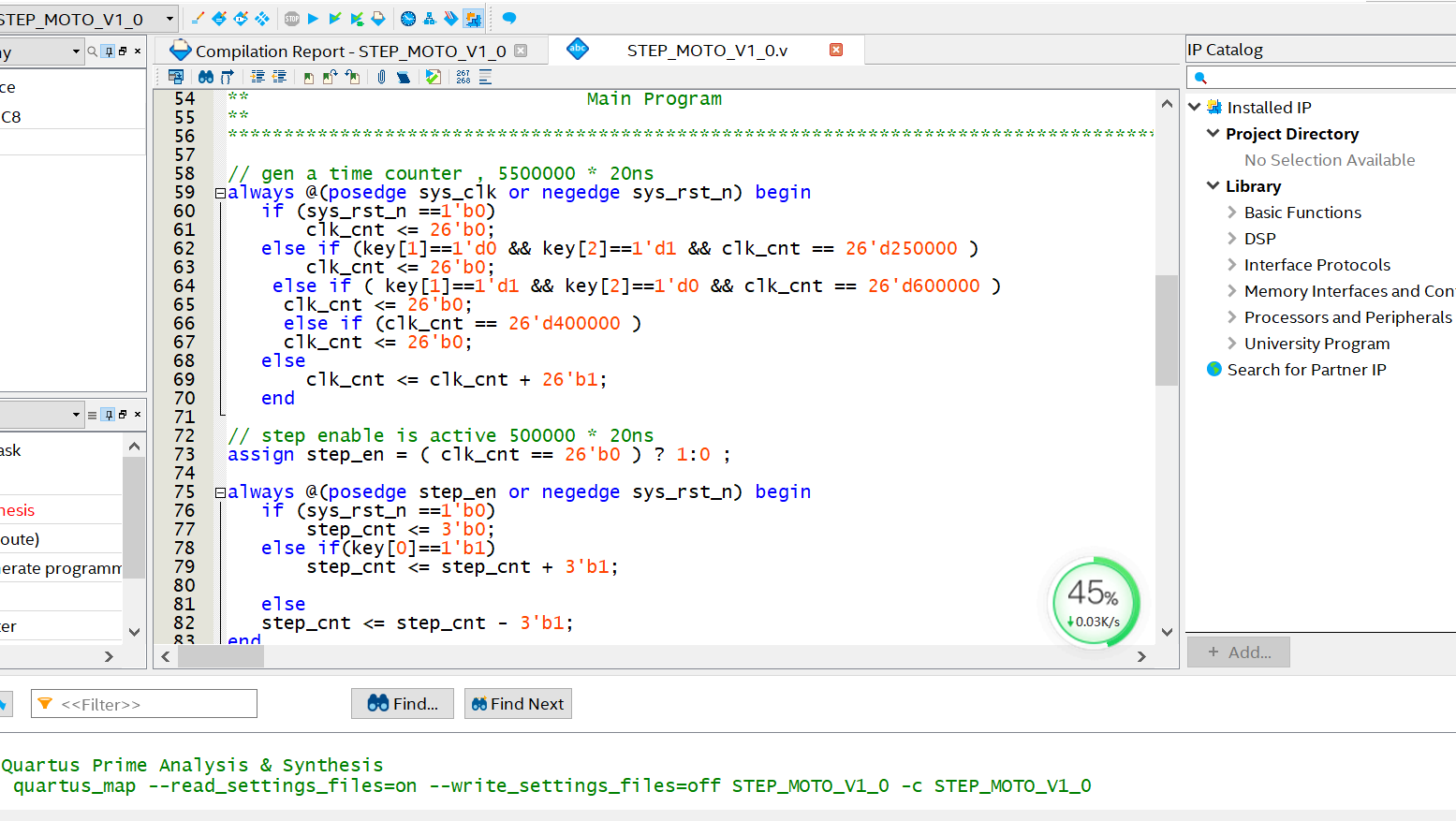

// gen a time counter , 5500000 * 20ns

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

clk_cnt <= 26'b0;

else if (key[1]==1'd0 && key[2]==1'd1 && clk_cnt == 26'd250000 )

clk_cnt <= 26'b0;

else if ( key[1]==1'd1 && key[2]==1'd0 && clk_cnt == 26'd600000 )

clk_cnt <= 26'b0;

else if (clk_cnt == 26'd400000 )

clk_cnt <= 26'b0;

else

clk_cnt <= clk_cnt + 26'b1;

end

// step enable is active 500000 * 20ns

assign step_en = ( clk_cnt == 26'b0 ) ? 1:0 ;

always @(posedge step_en or negedge sys_rst_n) begin

if

部分文件列表

| 文件名 | 文件大小 | 修改时间 |

| STEP_MOTO_V2_0(EP4CE6)/db/altsyncram_4u14.tdf | 13KB | 2014-07-30 10:14:22 |

| STEP_MOTO_V2_0(EP4CE6)/db/altsyncram_8u14.tdf | 13KB | 2014-07-30 10:15:50 |

| STEP_MOTO_V2_0(EP4CE6)/db/altsyncram_s024.tdf | 37KB | 2014-07-30 10:12:06 |

| STEP_MOTO_V2_0(EP4CE6)/db/cmpr_ngc.tdf | 2KB | 2014-07-30 10:12:08 |

| STEP_MOTO_V2_0(EP4CE6)/db/cmpr_pgc.tdf | 2KB | 2014-07-30 10:14:22 |

| STEP_MOTO_V2_0(EP4CE6)/db/cmpr_rgc.tdf | 2KB | 2014-07-30 10:12:08 |

| STEP_MOTO_V2_0(EP4CE6)/db/cntr_23j.tdf | 3KB | 2014-07-30 10:12:08 |

| STEP_MOTO_V2_0(EP4CE6)/db/cntr_cgi.tdf | 4KB | 2014-07-30 10:12:08 |

| STEP_MOTO_V2_0(EP4CE6)/db/cntr_egi.tdf | 4KB | 2014-07-30 10:12:08 |

| STEP_MOTO_V2_0(EP4CE6)/db/cntr_g9j.tdf | 4KB | 2014-07-30 10:12:08 |

| STEP_MOTO_V2_0(EP4CE6)/db/cntr_igi.tdf | 4KB | 2014-07-30 10:15:50 |

| ... | ||

最新上传

-

21ic下载 打赏310.00元 2天前

用户:mulanhk

-

21ic下载 打赏310.00元 2天前

用户:lanmukk

-

21ic下载 打赏310.00元 2天前

用户:zhengdai

-

21ic下载 打赏240.00元 2天前

用户:江岚

-

21ic下载 打赏240.00元 2天前

用户:潇潇江南

-

21ic下载 打赏210.00元 2天前

用户:gsy幸运

-

21ic下载 打赏70.00元 2天前

用户:小猫做电路

-

21ic下载 打赏120.00元 2天前

用户:jh0355

-

21ic下载 打赏110.00元 2天前

用户:jh03551

-

21ic下载 打赏70.00元 2天前

用户:liqiang9090

-

21ic下载 打赏45.00元 2天前

用户:有理想666

-

21ic下载 打赏20.00元 2天前

用户:w178191520

-

21ic下载 打赏40.00元 2天前

用户:烟雨

-

21ic下载 打赏20.00元 2天前

用户:eaglexiong

-

21ic下载 打赏20.00元 2天前

用户:sun2152

-

21ic下载 打赏20.00元 2天前

用户:xuzhen1

-

21ic下载 打赏15.00元 2天前

用户:kk1957135547

-

21ic下载 打赏15.00元 2天前

用户:w993263495

-

21ic下载 打赏15.00元 2天前

用户:x15580286248

-

21ic下载 打赏15.00元 2天前

用户:w1966891335

-

小猫做电路 打赏830.00元 3天前

-

gsy幸运 打赏880.00元 3天前

-

zhengdai 打赏730.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:STM32智能交流电检测

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏15.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

全部评论(0)