- 1

- 2

- 3

- 4

- 5

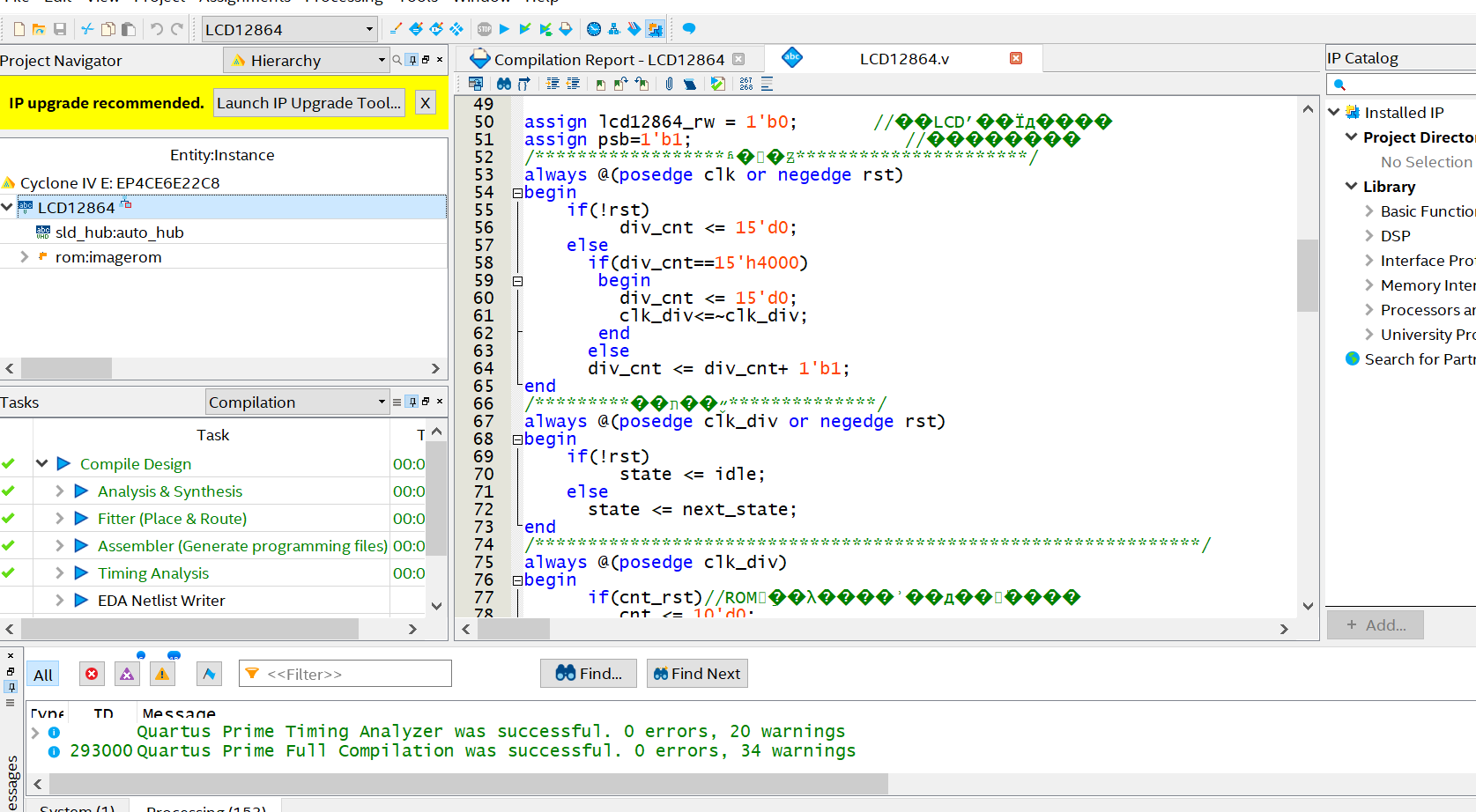

FPGA控制LCD12864显示屏显示图片实验Verilog逻辑源码Quartus11.0工程文件

资料介绍

FPGA控制LCD12864显示屏显示图片实验Verilog逻辑源码Quartus11.0工程文件, FPGA型号为CYCLONE4E系列中的EP4CE6E22C8,可以做为你的学习设计参考。

module LCD12864(clk,rst,lcd12864_rs,lcd12864_rw,lcd12864_en,lcd12864_data,psb);

input clk; //系统时钟

input rst; //复位信号

output lcd12864_rs; //1:数据模式;0:指令模式

output lcd12864_rw; //1:读操作;0:写操作

output lcd12864_en; //使能信号,写操作时在下降沿将数据送出;读操作时保持高电平

output psb;

output[7:0] lcd12864_data; //LCD数据总线

reg lcd12864_rs;

reg lcd12864_en;

reg[7:0] lcd12864_data;

reg[3:0] state; //状态机

reg[3:0] next_state;

reg[14:0] div_cnt; //分频计数器

reg[9:0] cnt; //写操作计数器

reg cnt_rst; //写操作计数器复位信号

wire[7:0] data; //要显示的数据

reg clk_div; //分频时钟

/********************状态机参数*********************/

parameter idle = 4'b0000,

setbase_1 = 4'b0001,

setmode_1 = 4'b0010,

setcurs_1 = 4'b0111,

setexte_1 = 4'b0100,

setexte_2 = 4'b1100,

wr_y_addr_1 = 4'b1101,

wr_y_addr_2 = 4'b1111,

wr_x_addr_1 = 4'b1110,

wr_x_addr_2 = 4'b1010,

wr_data_1 = 4'b1011,

wr_data_2 = 4'b1001;

assign lcd12864_rw = 1'b0; //对LCD始终为写操作

assign psb=1'b1; //开背光灯

/******************时钟分频**********************/

always @(posedge clk or negedge rst)

begin

if(!rst)

div_cnt <= 15'd0;

else

if(div_cnt==15'h4000)

begin

div_cnt <= 15'd0;

clk_div<=~clk_div;

end

else

div_cnt <= div_cnt+ 1'b1;

end

/**************状态机转向*********/

always @(posedge clk_div or negedge rst)

begin

if(!rst)

state <= idle;

else

state <= next_state;

end

/***************************************************************/

always @(posedge clk_div)

begin

if(cnt_rst)//ROM寻址复位,表示已写入一帧数据

cnt <= 10'd0;

else if(state == wr_data_2)//每写入一字节数据,地址加一

cnt <= cnt + 1'b1;

end

/**********************状态机逻辑*******************************/

always @(state or cnt

部分文件列表

| 文件名 | 大小 |

| lab6_LCD12864display_picture/ | |

| lab6_LCD12864display_picture/LCD12864.asm.rpt | 9KB |

| lab6_LCD12864display_picture/LCD12864.cdf | |

| lab6_LCD12864display_picture/LCD12864.done | |

| lab6_LCD12864display_picture/LCD12864.fit.rpt | |

| lab6_LCD12864display_picture/LCD12864.fit.smsg | 1KB |

| lab6_LCD12864display_picture/LCD12864.fit.summary | 1KB |

| lab6_LCD12864display_picture/LCD12864.flow.rpt | |

| lab6_LCD12864display_picture/LCD12864.jdi | 6KB |

| lab6_LCD12864display_picture/LCD12864.map.rpt | |

| lab6_LCD12864display_picture/LCD12864.map.summary | |

| ... | |

最新上传

-

zhengdai 打赏1000.00元 3天前

资料:STM32IAP使用说明

-

gsy幸运 打赏955.00元 3天前

资料:STM32IAP使用说明

-

小猫做电路 打赏855.00元 3天前

资料:STM32IAP使用说明

-

21ic小能手 打赏310.00元 3天前

用户:zhengdai

-

21ic小能手 打赏320.00元 3天前

用户:liqiang9090

-

21ic小能手 打赏310.00元 3天前

用户:gsy幸运

-

21ic小能手 打赏270.00元 3天前

用户:jh03551

-

21ic小能手 打赏240.00元 3天前

用户:小猫做电路

-

21ic小能手 打赏210.00元 3天前

用户:w178191520

-

21ic小能手 打赏90.00元 3天前

用户:kkfjenui

-

21ic小能手 打赏60.00元 3天前

用户:liao6

-

21ic小能手 打赏60.00元 3天前

用户:w1966891335

-

21ic小能手 打赏90.00元 3天前

用户:jh0355

-

21ic小能手 打赏30.00元 3天前

用户:xuzhen1

-

21ic小能手 打赏30.00元 3天前

用户:sun2152

-

21ic小能手 打赏50.00元 3天前

用户:xzxbybd

-

21ic小能手 打赏50.00元 3天前

用户:mulanhk

-

21ic小能手 打赏20.00元 3天前

用户:x15580286248

-

21ic小能手 打赏15.00元 3天前

用户:w993263495

-

21ic小能手 打赏30.00元 3天前

用户:玉落彼岸

-

21ic小能手 打赏20.00元 3天前

用户:铁蛋锅

-

21ic小能手 打赏10.00元 3天前

用户:zmcch

-

21ic小能手 打赏10.00元 3天前

-

21ic下载 打赏1.00元 3天前

用户:zzcyolo

-

21ic下载 打赏1.00元 3天前

用户:玉落彼岸

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

sdqdjqk 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

wisdomlin 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

799902619 打赏1.00元 3天前

资料:新立新龙软件

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

全部评论(0)