- 1

- 2

- 3

- 4

- 5

USB FT245BM_test fpga控制逻辑Verilog HDL源码文件 已在项目测试使用

资料介绍

USB FT245BM_test fpga控制逻辑Verilog HDL源码文件,已在项目测试使用,可以做为你的设计参考。

module FT245BM_test(

input wire rst_in, //板上复位信号

input wire clk_in, //40M晶振

output wire rtl8208b_rst, //rtl8208B复位信号

//DVI接口

input wire pclk,

input wire vs,

input wire blank,

input wire [7:0] rdata,

input wire [7:0] gdata,

input wire [7:0] bdata,

//USB接口

input wire RXF_n,

output wire RD_n,

inout tri [7:0] usb_dd,

input wire TXE_n,

output wire WR,

output reg [63:0] data_num,

//SDRAM接口

/* output wire sa_clk,

output wire [4:0] sa_cnt,

output wire [3:0] sa_dqm,

output wire [11:0] sa_addr,

output wire [1:0] sa_bank,

inout wire [31:0] sa_data,

//百兆发送口

input wire refclk,

output wire tx_en_a, //外口下行

output wire [5:0] tx_data_a,

output wire tx_en_b, //内口下行

output wire [5:0] tx_data_b,

input wire rx_mii_a, //外口上行

input wire [1:0] rd_mii_a,

input wire rx_mii_b, //内口上行

input wire [1:0] rd_mii_b,

inout tri sda,

output wire scl,

output wire wp,

*/

//其他接口

output wire [7:0] test_port,

output wire led_g,

output wire led_r,

output wire led_g_a, //机壳指示灯

output wire led_r_a

);

wire [7:0] clk_out;

wire clk100M;

wire clk25M;

wire sa_clk;

wire rx_data_sync;

wire [7:0] rx_data;

wire tx_data_sync;

wire [7:0] tx_data;

wire tx_busy;

wire [7:0] data_to_usb;

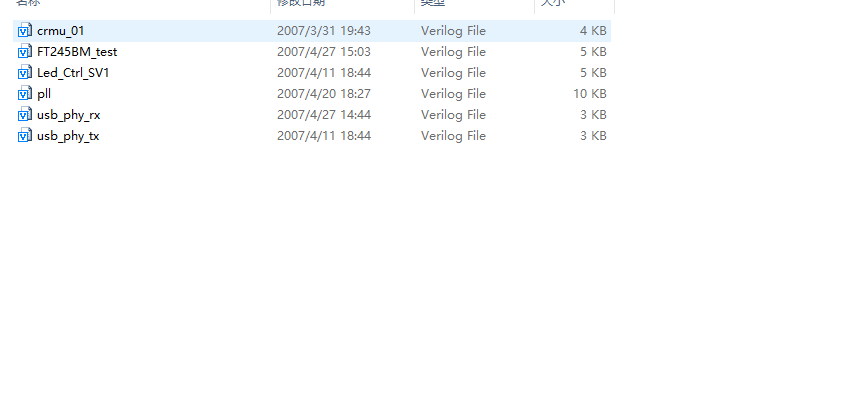

部分文件列表

| 文件名 | 大小 |

| FT245BM_test/design/ | |

| FT245BM_test/design/FT245BM_test.v | 4KB |

| FT245BM_test/design/Led_Ctrl_SV1.v | 4KB |

| FT245BM_test/design/crmu_01.v | 3KB |

| FT245BM_test/design/pll.v | 10KB |

| FT245BM_test/design/usb_phy_rx.v | 2KB |

| FT245BM_test/design/usb_phy_tx.v | 2KB |

| FT245BM_test/ |

最新上传

-

21ic小能手 打赏5.00元 2天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:gsy幸运

-

21ic下载 打赏310.00元 3天前

用户:小猫做电路

-

21ic下载 打赏360.00元 3天前

用户:mulanhk

-

21ic下载 打赏230.00元 3天前

用户:江岚

-

21ic下载 打赏230.00元 3天前

用户:潇潇江南

-

21ic下载 打赏210.00元 3天前

用户:zhengdai

-

21ic下载 打赏160.00元 3天前

用户:lanmukk

-

21ic下载 打赏130.00元 3天前

用户:jh03551

-

21ic下载 打赏110.00元 3天前

用户:liqiang9090

-

21ic下载 打赏110.00元 3天前

用户:jh0355

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏20.00元 3天前

用户:w178191520

-

21ic下载 打赏30.00元 3天前

用户:sun2152

-

21ic下载 打赏30.00元 3天前

用户:xuzhen1

-

21ic下载 打赏20.00元 3天前

用户:w993263495

-

21ic下载 打赏15.00元 3天前

用户:kk1957135547

-

21ic下载 打赏15.00元 3天前

用户:eaglexiong

-

21ic下载 打赏15.00元 3天前

用户:w1966891335

-

21ic下载 打赏25.00元 3天前

用户:烟雨

-

21ic下载 打赏75.00元 3天前

用户:有理想666

-

21ic下载 打赏10.00元 3天前

用户:x15580286248

-

21ic下载 打赏40.00元 3天前

用户:xzxbybd

-

21ic下载 打赏10.00元 3天前

-

21ic下载 打赏10.00元 3天前

用户:sfgplj123

-

21ic下载 打赏10.00元 3天前

用户:dadengpao

-

21ic小能手 打赏10.00元 3天前

资料:自己编写的CRC校验工具

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

shenzhenliugang 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

全部评论(1)

2024-08-30 16:22:56infowei

资料不错,谢谢!