- 1

- 2

- 3

- 4

- 5

FPGA读写sd卡实验Verilog逻辑源码Quartus工程文件+文档说明 FPGA型号Cyclo

资料介绍

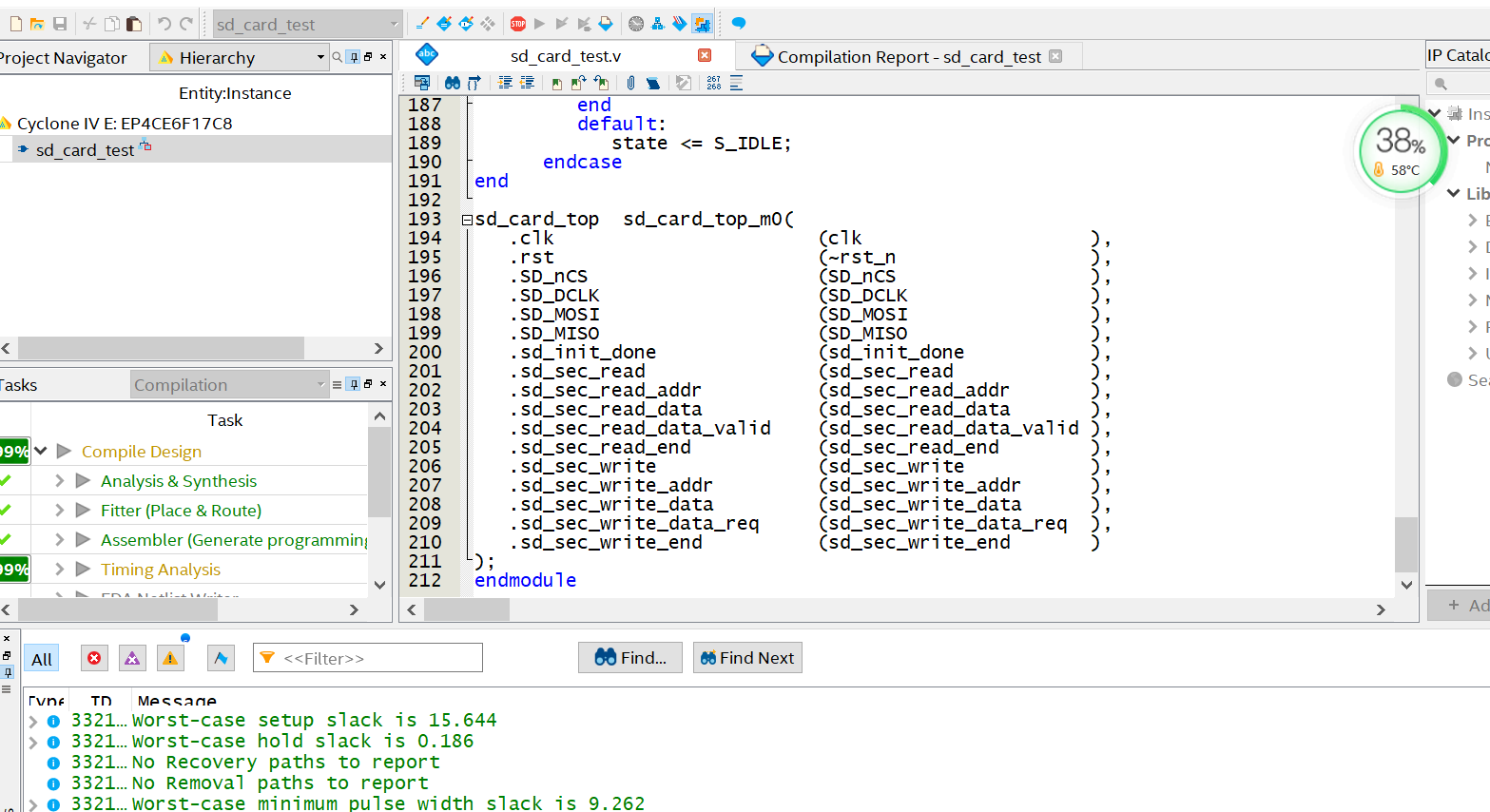

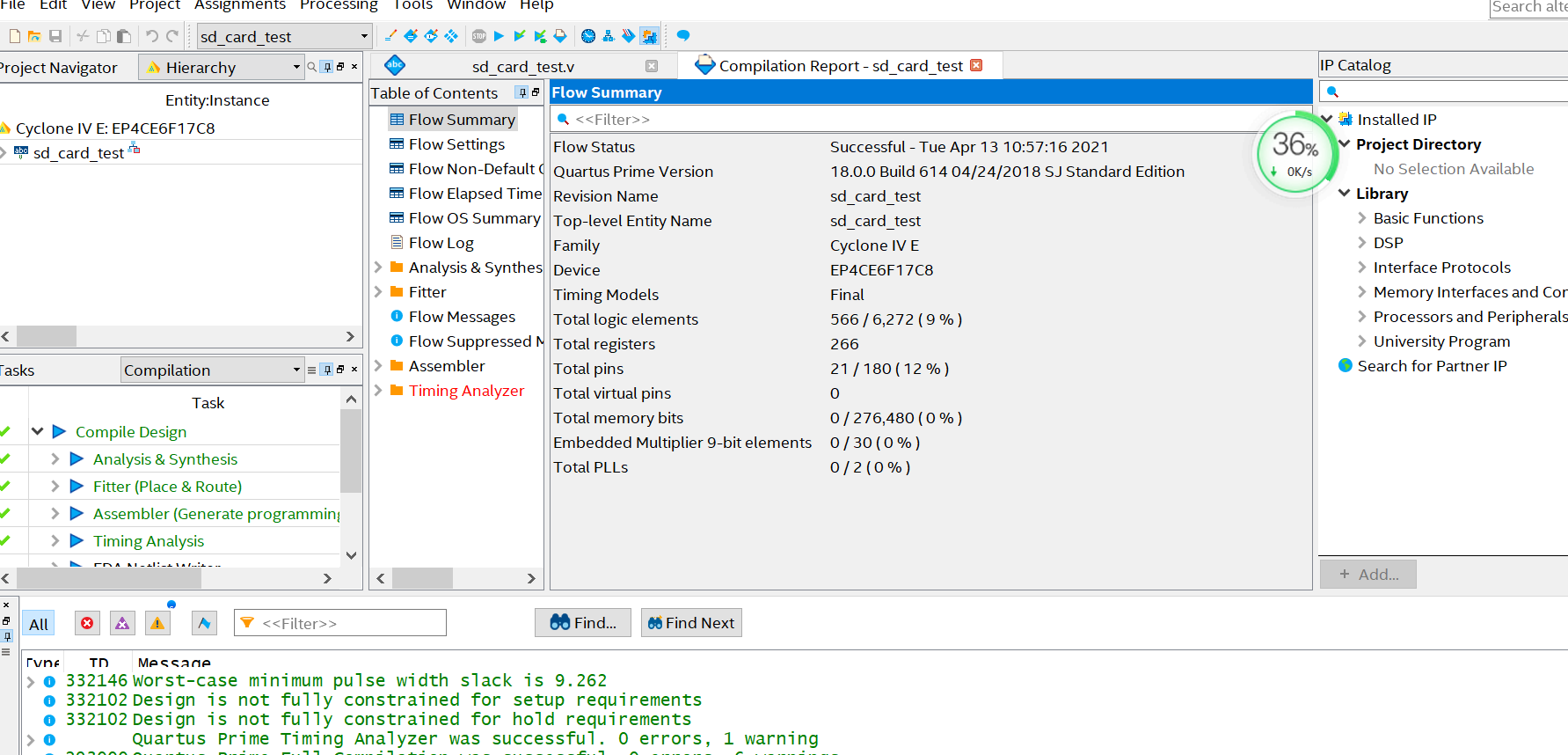

FPGA读写sd卡实验Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

module sd_card_test(

input clk,

input rst_n,

input key1,

output SD_nCS,

output SD_DCLK,

output SD_MOSI,

input SD_MISO,

output [5:0] seg_sel,

output [7:0] seg_data

);

parameter S_IDLE = 0;

parameter S_READ = 1;

parameter S_WRITE = 2;

parameter S_END = 3;

reg[3:0] state;

wire sd_init_done;

reg sd_sec_read;

wire[31:0] sd_sec_read_addr;

wire[7:0] sd_sec_read_data;

wire sd_sec_read_data_valid;

wire sd_sec_read_end;

reg sd_sec_write;

wire[31:0] sd_sec_write_addr;

reg [7:0] sd_sec_write_data;

wire sd_sec_write_data_req;

wire sd_sec_write_end;

reg[9:0] wr_cnt;

reg[9:0] rd_cnt;

wire button_negedge;

reg[7:0] read_data;

ax_debounce ax_debounce_m0

(

.clk (clk),

.rst (~rst_n),

.button_in (key1),

.button_posedge (),

.button_negedge (button_negedge),

.button_out ()

);

wire[6:0] seg_data_0;

seg_decoder seg_decoder_m0(

.bin_data (read_data[3:0]),

.seg_data (seg_data_0)

);

wire[6:0] seg_data_1;

seg_decoder seg_decoder_m1(

.bin_data (read_data[7:4]),

.seg_data (seg_data_1)

);

seg_scan seg_scan_m0(

.clk (clk),

.rst_n (rst_n),

.seg_sel (seg_sel),

.seg_data (seg_data),

.seg_data_0 ({1'b1,7'b1111_111}),

.seg_data_1 ({1'b1,7'b1111_111}),

.seg_data_2 ({1'b1,7'b1111_111}),

.seg_data_3 ({1'b1,7'b1111_111}),

.seg_data_4 ({1'b1,seg_data_1}),

.seg_data_5 ({sd_init_done,seg_data_0})

);

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

wr_cnt <= 10'd0;

else if(state == S_WRITE)

begin

if(sd_sec_write_data_req == 1'b1)

wr_cnt <= wr_cnt + 10'd1;

end

else

wr_cnt <= 10'd0;

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

rd_cnt <= 10'd0;

else if(state == S_READ)

begin

if(sd_sec_read_data_valid == 1'b1)

rd_cnt <= rd_cnt + 10'd1;

end

else

rd_cnt <= 10'd0;

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

read_data <= 8'd0;

else if(state == S_READ)

begin

if(sd_sec_read_data_valid == 1'b1 && rd_cnt == 10'd0)

read_data <= sd_sec_read_data;

end

else if(state == S_END && button_negedge == 1'b1)

read_data <= read_data + 8'd1;

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

sd_sec_write_data <= 8'd0;

else if(sd_sec_write_data_req)

sd_sec_write_data <= read_data +

部分文件列表

| 文件名 | 大小 |

| 14.sd卡读写实验.pdf | 1205KB |

| 14_sd_card_test/ | |

| 14_sd_card_test/ax301_ax4010_base.tcl | 1KB |

| 14_sd_card_test/db/ | |

| 14_sd_card_test/db/.cmp.kpt | |

| 14_sd_card_test/db/altsyncram_6b24.tdf | |

| 14_sd_card_test/db/altsyncram_7b24.tdf | |

| 14_sd_card_test/db/altsyncram_8b24.tdf | |

| 14_sd_card_test/db/altsyncram_9b24.tdf | |

| 14_sd_card_test/db/altsyncram_ab24.tdf | |

| 14_sd_card_test/db/altsyncram_cb24.tdf | |

| ... | |

最新上传

-

21ic下载 打赏310.00元 1天前

用户:mulanhk

-

21ic下载 打赏310.00元 1天前

用户:lanmukk

-

21ic下载 打赏310.00元 1天前

用户:zhengdai

-

21ic下载 打赏240.00元 1天前

用户:江岚

-

21ic下载 打赏240.00元 1天前

用户:潇潇江南

-

21ic下载 打赏210.00元 1天前

用户:gsy幸运

-

21ic下载 打赏70.00元 1天前

用户:小猫做电路

-

21ic下载 打赏120.00元 1天前

用户:jh0355

-

21ic下载 打赏110.00元 1天前

用户:jh03551

-

21ic下载 打赏70.00元 1天前

用户:liqiang9090

-

21ic下载 打赏45.00元 1天前

用户:有理想666

-

21ic下载 打赏20.00元 1天前

用户:w178191520

-

21ic下载 打赏40.00元 1天前

用户:烟雨

-

21ic下载 打赏20.00元 1天前

用户:eaglexiong

-

21ic下载 打赏20.00元 1天前

用户:sun2152

-

21ic下载 打赏20.00元 1天前

用户:xuzhen1

-

21ic下载 打赏15.00元 1天前

用户:kk1957135547

-

21ic下载 打赏15.00元 1天前

用户:w993263495

-

21ic下载 打赏15.00元 1天前

用户:x15580286248

-

21ic下载 打赏15.00元 1天前

用户:w1966891335

-

小猫做电路 打赏830.00元 3天前

-

gsy幸运 打赏880.00元 3天前

-

zhengdai 打赏730.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:STM32智能交流电检测

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏15.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

全部评论(0)