- 1

- 2

- 3

- 4

- 5

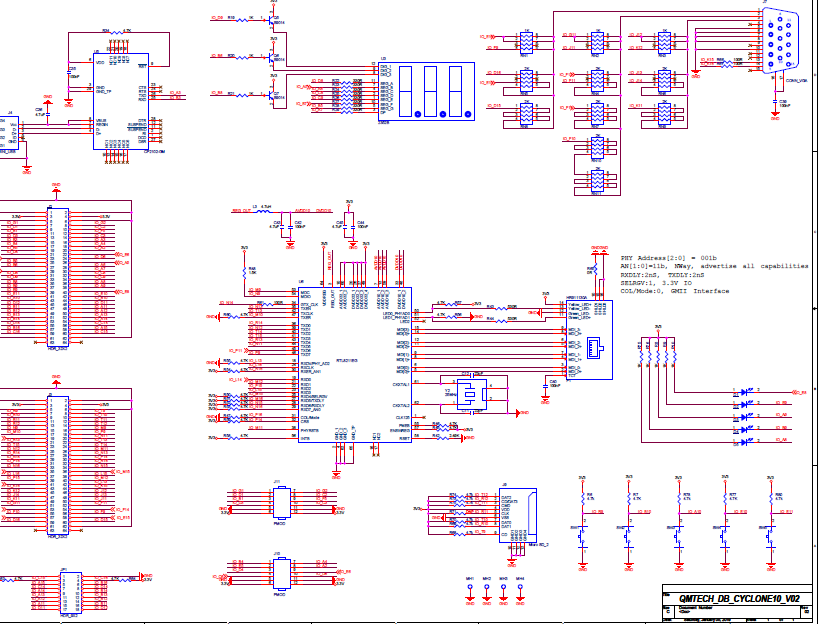

Altera(Intel)_Cyclone10_10CL006开发板资料硬件参考设计+逻辑例程

资料介绍

Altera(Intel)_Cyclone10_10CL006开发板资料硬件参考设计+逻辑例程。

QM_Cyclone10_10CL006开发板主要特征参数如下所示:

主控FPGA:10CL006YU256C8G;

主控FPGA外部时钟源频率:50MHz;

10CL006YU256C8G芯片内部自带丰富的Block RAM资源;

10CL006YU256C8G芯片逻辑单元数为6K LE;

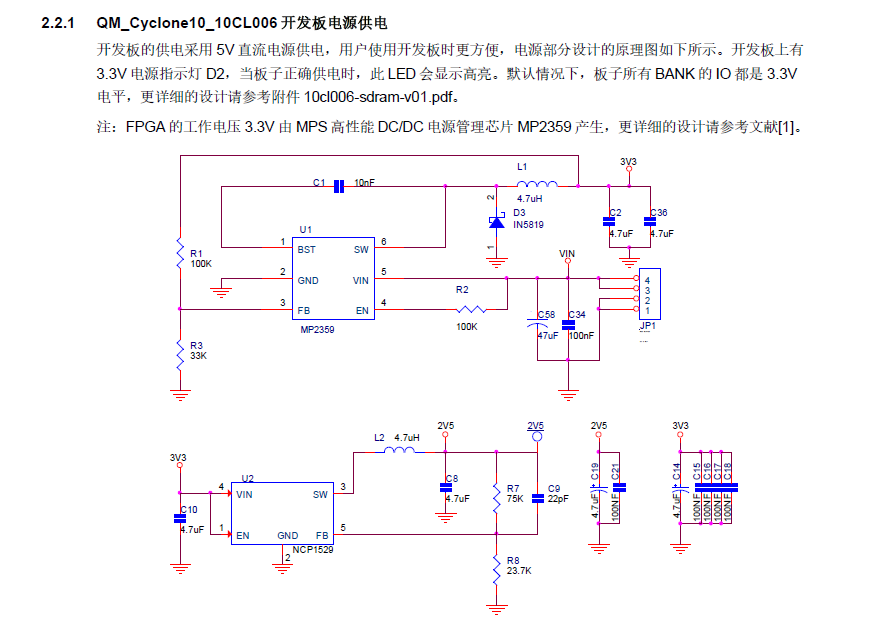

QM_Cyclone10_10CL006开发板板载MP2359高效率DC/DC提供FPGA芯片工作的3.3V电源;

QM_Cyclone10_10CL006开发板引出了两排64p、2.54mm间距的排座,可以用于外接24Bit的TFT液晶屏、CY7C68013 USB模块、高速ADC采集模块或者CMOS摄像头模块等;

QM_Cyclone10_10CL006开发板引出了芯片的3路按键用于测试;

QM_Cyclone10_10CL006开发板引出了芯片的2路LED用于测试;

QM_Cyclone10_10CL006开发板引出了芯片的JTAG调试端口,采用双排10p、2.54mm的排针;

部分文件列表

| 文件名 | 大小 |

| Datasheet/ | |

| Datasheet/aib-01029.pdf | |

| Datasheet/an800.pdf | |

| Datasheet/c10lp-51002.pdf | |

| Datasheet/c10lp-51003.pdf | 1180KB |

| Datasheet/c10lp-eval-a1-sch.PDF | |

| Datasheet/cyclone-10-lp-product-table.pdf | |

| Datasheet/pcg-01021.pdf | |

| Hardware/ | |

| Hardware/10cl006-sdram-v01.pdf | |

| Hardware/db-fpga-10cl006-v01.pdf | |

| ... | |

最新上传

-

21ic小能手 打赏10.00元 1天前

-

21ic小能手 打赏10.00元 1天前

-

21ic小能手 打赏10.00元 2天前

-

sdqdjqk 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

wisdomlin 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

799902619 打赏1.00元 3天前

资料:新立新龙软件

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

资料:智谱开源AutoGLM

-

21ic下载 打赏310.00元 3天前

用户:jh0355

-

21ic下载 打赏310.00元 3天前

用户:zhengdai

-

21ic下载 打赏310.00元 3天前

用户:gsy幸运

-

21ic下载 打赏230.00元 3天前

用户:小猫做电路

-

21ic下载 打赏210.00元 3天前

用户:w178191520

-

21ic下载 打赏60.00元 3天前

用户:jh03551

-

21ic下载 打赏90.00元 3天前

用户:铁蛋锅

-

21ic下载 打赏80.00元 3天前

用户:xzxbybd

-

21ic下载 打赏60.00元 3天前

用户:kk1957135547

-

21ic下载 打赏60.00元 3天前

用户:w1966891335

-

21ic下载 打赏60.00元 3天前

用户:w993263495

-

21ic下载 打赏60.00元 3天前

用户:sun2152

-

21ic下载 打赏60.00元 3天前

用户:xuzhen1

-

21ic下载 打赏60.00元 3天前

用户:liao6

-

21ic下载 打赏70.00元 3天前

用户:liqiang9090

-

21ic下载 打赏70.00元 3天前

用户:mulanhk

-

21ic下载 打赏20.00元 3天前

用户:x15580286248

-

21ic下载 打赏30.00元 3天前

用户:玉落彼岸

-

21ic下载 打赏5.00元 3天前

用户:hnygpx

-

21ic下载 打赏10.00元 3天前

用户:vikey_zhu

全部评论(2)

2021-04-14 12:05:54wqc1999

非常有用

2020-10-11 17:12:07汉水之子

谢ziyuan,SDRAM部分有帮助