- 1

- 2

- 3

- 4

- 5

LCD1602屏 (EP4CE30) FPGA读写实验Verilog逻辑源码Quartus工程文件+

资料介绍

LCD1602屏 (EP4CE30) FPGA读写实验Verilog逻辑源码Quartus工程文件+文档资料。FPGA为CYCLONE4系列中的EP4CE30F23C8. 完整的工程文件,可以做为你的学习设计参考。

module LCD1602_Cnt(input sys_clk, //50M

input sys_rst_n,

output reg lcd_rs, //0:write order; 1:write data

output lcd_rw, //0:write data; 1:read data

output reg lcd_en, //

output reg [7:0] lcd_data);

//--------------------lcd1602 order----------------------------

parameter Mode_Set = 8'h38, //������ʾģʽ��8λ2��5x8����

Cursor_Set = 8'h0c, //��ʾ������겻��ʾ�����겻������˸

Address_Set = 8'h06, //���ֲ����������Զ�����

Clear_Set = 8'h01; //��������긴λ

/****************************LCD1602 Display Data****************************/

wire [7:0] data0,data1; //counter data

wire [7:0] addr; //write address

//---------------------------------1s counter-----------------------------------

reg [25:0] cnt1;

reg [7:0] data_r0,data_r1;

always@(posedge sys_clk or negedge sys_rst_n)

begin

if(!sys_rst_n)

begin

cnt1 <= 1'b0;

data_r0 <= 1'b0;

data_r1 <= 1'b0;

end

else if(cnt1==26'd50000000)

begin

if(data_r0==8'd9)

begin

data_r0 <= 1'b0;

if(data_r1==8'd9)

data_r1 <= 1'b0;

else

data_r1 <= data_r1 + 1'b1;

end

else

data_r0 <= data_r0 + 1'b1;

cnt1 <= 1'b0;

end

else

cnt1 <= cnt1 + 1'b1;

end

assign data0 = 8'h30 + data_r0 ;

assign data1 = 8'h30 + data_r1 ;

//-------------------address------------------

assign addr = 8'h80;

/****************************LCD1602 Driver****************************/

//-----------------------lcd1602 sys_clk_en---------------------

reg

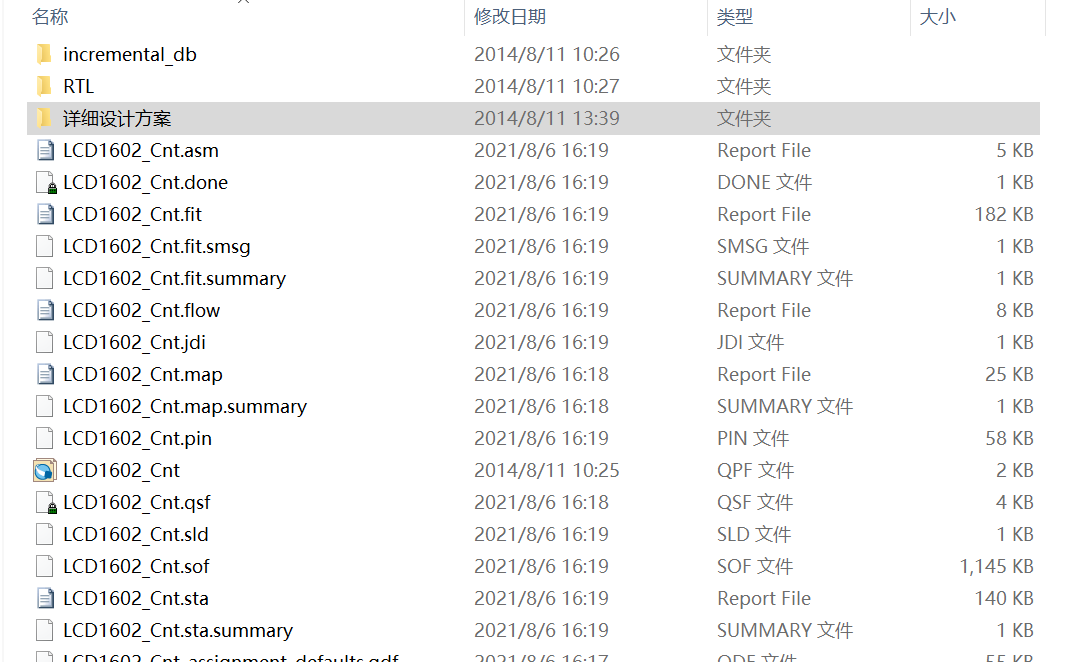

部分文件列表

| 文件名 | 文件大小 | 修改时间 |

| LCD1602_Cnt/db/LCD1602_Cnt.(0).cnf.cdb | 9KB | 2014-08-11 13:22:30 |

| LCD1602_Cnt/db/LCD1602_Cnt.(0).cnf.hdb | 2KB | 2014-08-11 13:22:30 |

| LCD1602_Cnt/db/LCD1602_Cnt.amm.cdb | 1KB | 2014-08-11 13:08:28 |

| LCD1602_Cnt/db/LCD1602_Cnt.asm.qmsg | 2KB | 2014-08-11 13:08:38 |

| LCD1602_Cnt/db/LCD1602_Cnt.asm.rdb | 1KB | 2014-08-11 13:08:38 |

| LCD1602_Cnt/db/LCD1602_Cnt.cbx.xml | 1KB | 2014-08-11 13:22:30 |

| LCD1602_Cnt/db/LCD1602_Cnt.cmp.kpt | 1KB | 2014-08-11 13:08:34 |

| LCD1602_Cnt/db/LCD1602_Cnt.cmp.rdb | 5KB | 2014-08-11 13:22:32 |

| LCD1602_Cnt/db/LCD1602_Cnt.cmp_merge.kpt | 1KB | 2014-08-11 13:22:32 |

| LCD1602_Cnt/db/LCD1602_Cnt.cycloneive_io_sim_cache.31um_ff_1200mv_0c_fast.hsd | 729KB | 2014-08-11 13:08:38 |

| LCD1602_Cnt/db/LCD1602_Cnt.cycloneive_io_sim_cache.31um_ss_1200mv_0c_slow.hsd | 722KB | 2014-08-11 13:08:38 |

| ... | ||

最新上传

-

21ic小能手 打赏5.00元 1天前

-

21下载积分 打赏1.00元 1天前

用户:德才兼备

-

mulanhk 打赏1.00元 2天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:数控电子负载-CH552

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:zhengdai

-

21ic下载 打赏310.00元 3天前

用户:liqiang9090

-

21ic下载 打赏330.00元 3天前

用户:jh0355

-

21ic下载 打赏210.00元 3天前

用户:小猫做电路

-

21ic下载 打赏240.00元 3天前

用户:jh03551

-

21ic下载 打赏210.00元 3天前

用户:gsy幸运

-

21ic下载 打赏70.00元 3天前

用户:w178191520

-

21ic下载 打赏60.00元 3天前

用户:sun2152

-

21ic下载 打赏80.00元 3天前

用户:江岚

-

21ic下载 打赏60.00元 3天前

用户:xuzhen1

-

21ic下载 打赏20.00元 3天前

用户:kk1957135547

-

21ic下载 打赏40.00元 3天前

用户:潇潇江南

-

21ic下载 打赏20.00元 3天前

用户:w993263495

-

21ic下载 打赏20.00元 3天前

用户:w1966891335

-

21ic下载 打赏70.00元 3天前

用户:有理想666

-

21ic下载 打赏35.00元 3天前

用户:xzxbybd

-

21ic下载 打赏15.00元 3天前

用户:x15580286248

-

21ic下载 打赏25.00元 3天前

用户:铁蛋锅

-

21ic下载 打赏35.00元 3天前

用户:mulanhk

全部评论(0)