- 1

- 2

- 3

- 4

- 5

基于FPGA设计的 AD9708 +AD9280 ADDA转换测试Verilog逻辑源码Quartu

资料介绍

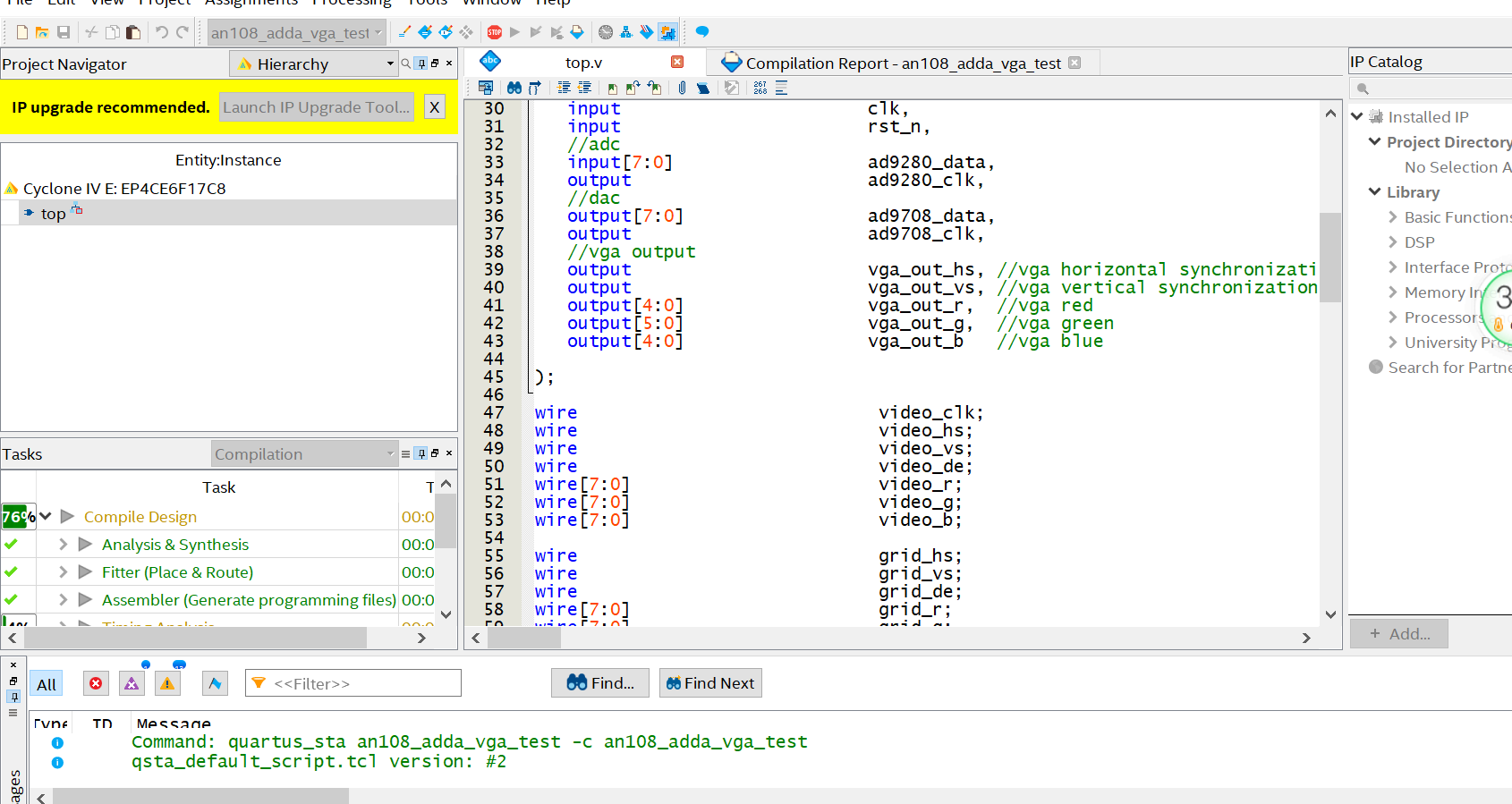

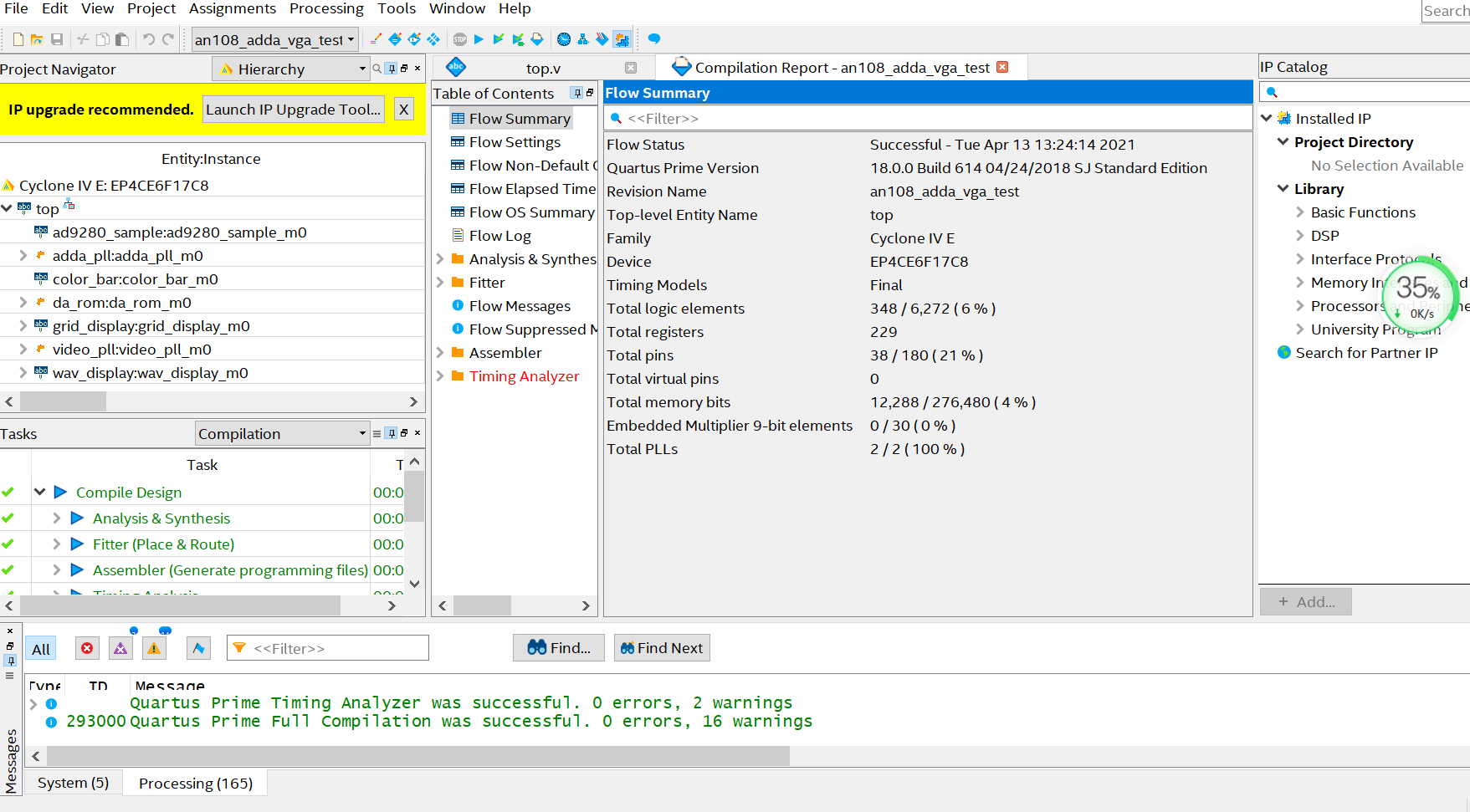

基于FPGA设计的 AD9708 +AD9280 ADDA转换测试Verilog逻辑源码Quartus工程文件+文档说明,DA芯片选用AD公司推出的AD9708,AD芯片选用AD9280,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

module top(

input clk,

input rst_n,

//adc

input[7:0] ad9280_data,

output ad9280_clk,

//dac

output[7:0] ad9708_data,

output ad9708_clk,

//vga output

output vga_out_hs, //vga horizontal synchronization

output vga_out_vs, //vga vertical synchronization

output[4:0] vga_out_r, //vga red

output[5:0] vga_out_g, //vga green

output[4:0] vga_out_b //vga blue

);

wire video_clk;

wire video_hs;

wire video_vs;

wire video_de;

wire[7:0] video_r;

wire[7:0] video_g;

wire[7:0] video_b;

wire grid_hs;

wire grid_vs;

wire grid_de;

wire[7:0] grid_r;

wire[7:0] grid_g;

wire[7:0] grid_b;

wire wave0_hs;

wire wave0_vs;

wire wave0_de;

wire[7:0] wave0_r;

wire[7:0] wave0_g;

wire[7:0] wave0_b;

wire adc_clk;

wire adc0_buf_wr;

wire[10:0] adc0_buf_addr;

wire[7:0] adc0_buf_data;

wire dac_clk;

wire[7:0] dac_data;

reg[8:0] rom_addr;

assign vga_out_hs = wave0_hs;

assign vga_out_vs = wave0_vs;

assign vga_out_r = wave0_r[7:3]; //discard low bit data

assign vga_out_g = wave0_g[7:2]; //discard low bit data

assign vga_out_b = wave0_b[7:3]; //discard low bit data

assign ad9280_clk = adc_clk;

assign ad9708_clk = dac_clk;

assign ad9708_data = dac_data;

//generate video pixel clock

video_pll video_pll_m0(

.inclk0(clk),

.c0(video_clk));

adda_pll adda_pll_m0(

.inclk0(clk),

.c0(dac_clk),

.c1(adc_clk),

);

color_bar color_bar_m0(

.clk(video_clk),

.rst(~rst_n),

.hs(video_hs),

.vs(video_vs),

.de(video_de),

.rgb_r(video_r),

.rgb_g(video_g),

.rgb_b(video_b)

);

部分文件列表

| 文件名 | 大小 |

| 26.ADDA测试例程.pdf | 1220KB |

| 26_an108_adda_vga_test/ | |

| 26_an108_adda_vga_test/PLLJ_PLLSPE_INFO.txt | |

| 26_an108_adda_vga_test/an108_adda_vga_test.ipregen.rpt | 4KB |

| 26_an108_adda_vga_test/an108_adda_vga_test.jdi | 4KB |

| 26_an108_adda_vga_test/an108_adda_vga_test.qpf | |

| 26_an108_adda_vga_test/an108_adda_vga_test.qsf | 4KB |

| 26_an108_adda_vga_test/an108_adda_vga_test.sdc | 1KB |

| 26_an108_adda_vga_test/an108_adda_vga_test_assignment_defaults.qdf | |

| 26_an108_adda_vga_test/db/ | |

| 26_an108_adda_vga_test/db/.cmp.kpt | |

| ... | |

最新上传

-

21ic下载 打赏310.00元 2天前

用户:mulanhk

-

21ic下载 打赏310.00元 2天前

用户:lanmukk

-

21ic下载 打赏310.00元 2天前

用户:zhengdai

-

21ic下载 打赏240.00元 2天前

用户:江岚

-

21ic下载 打赏240.00元 2天前

用户:潇潇江南

-

21ic下载 打赏210.00元 2天前

用户:gsy幸运

-

21ic下载 打赏70.00元 2天前

用户:小猫做电路

-

21ic下载 打赏120.00元 2天前

用户:jh0355

-

21ic下载 打赏110.00元 2天前

用户:jh03551

-

21ic下载 打赏70.00元 2天前

用户:liqiang9090

-

21ic下载 打赏45.00元 2天前

用户:有理想666

-

21ic下载 打赏20.00元 2天前

用户:w178191520

-

21ic下载 打赏40.00元 2天前

用户:烟雨

-

21ic下载 打赏20.00元 2天前

用户:eaglexiong

-

21ic下载 打赏20.00元 2天前

用户:sun2152

-

21ic下载 打赏20.00元 2天前

用户:xuzhen1

-

21ic下载 打赏15.00元 2天前

用户:kk1957135547

-

21ic下载 打赏15.00元 2天前

用户:w993263495

-

21ic下载 打赏15.00元 2天前

用户:x15580286248

-

21ic下载 打赏15.00元 2天前

用户:w1966891335

-

小猫做电路 打赏830.00元 3天前

-

gsy幸运 打赏880.00元 3天前

-

zhengdai 打赏730.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:STM32智能交流电检测

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏15.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

全部评论(0)