- 1

- 2

- 3

- 4

- 5

FPGA实现DDS,f=90kHZ~5MHZ范围

资料介绍

FPGA实现DDS,f=90kHZ~5MHZ范围 FPGA实现DDS,f=90kHZ~5MHZ范围

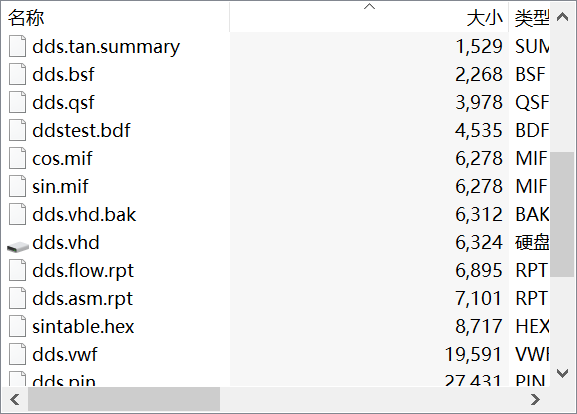

部分文件列表

| 文件名 | 文件大小 | 修改时间 |

| dds/cos.mif | 6KB | 2009-05-08 23:36:20 |

| dds/db/altsyncram_05p3.tdf | 3KB | 2009-05-04 21:57:54 |

| dds/db/altsyncram_0hq1.tdf | 46KB | 2009-05-04 22:16:30 |

| dds/db/altsyncram_4hq1.tdf | 95KB | 2009-05-04 22:13:18 |

| dds/db/altsyncram_5h11.tdf | 12KB | 2009-05-08 23:20:26 |

| dds/db/altsyncram_ceq1.tdf | 46KB | 2009-05-04 21:57:54 |

| dds/db/altsyncram_k7p3.tdf | 3KB | 2009-05-04 22:16:30 |

| dds/db/altsyncram_m121.tdf | 12KB | 2009-05-04 21:29:06 |

| dds/db/altsyncram_o7p3.tdf | 3KB | 2009-05-04 22:13:18 |

| dds/db/cntr_0ci.tdf | 4KB | 2009-05-04 22:13:22 |

| dds/db/cntr_2ci.tdf | 4KB | 2009-05-04 21:57:56 |

| ... | ||

最新上传

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

资料:智谱开源AutoGLM

-

21ic下载 打赏310.00元 3天前

用户:jh0355

-

21ic下载 打赏310.00元 3天前

用户:zhengdai

-

21ic下载 打赏310.00元 3天前

用户:gsy幸运

-

21ic下载 打赏230.00元 3天前

用户:小猫做电路

-

21ic下载 打赏210.00元 3天前

用户:w178191520

-

21ic下载 打赏60.00元 3天前

用户:jh03551

-

21ic下载 打赏90.00元 3天前

用户:铁蛋锅

-

21ic下载 打赏80.00元 3天前

用户:xzxbybd

-

21ic下载 打赏60.00元 3天前

用户:kk1957135547

-

21ic下载 打赏60.00元 3天前

用户:w1966891335

-

21ic下载 打赏60.00元 3天前

用户:w993263495

-

21ic下载 打赏60.00元 3天前

用户:sun2152

-

21ic下载 打赏60.00元 3天前

用户:xuzhen1

-

21ic下载 打赏60.00元 3天前

用户:liao6

-

21ic下载 打赏70.00元 3天前

用户:liqiang9090

-

21ic下载 打赏70.00元 3天前

用户:mulanhk

-

21ic下载 打赏20.00元 3天前

用户:x15580286248

-

21ic下载 打赏30.00元 3天前

用户:玉落彼岸

-

21ic下载 打赏5.00元 3天前

用户:hnygpx

-

21ic下载 打赏10.00元 3天前

用户:vikey_zhu

-

21ic下载 打赏5.00元 3天前

用户:fine0406

-

21ic小能手 打赏15.00元 3天前

-

21ic小能手 打赏15.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

全部评论(0)