- 1

- 2

- 3

- 4

- 5

4位异步二进制减法计数器,利用QUARTUS II 9的CPLD_FPGA

资料介绍

4位异步二进制减法计数器,利用QUARTUS II 9的CPLD_FPGA

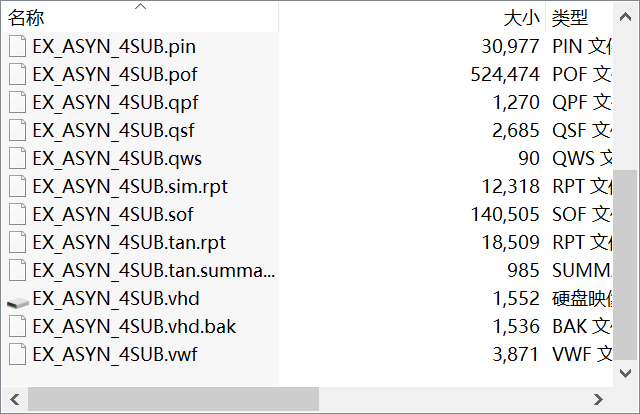

部分文件列表

| 文件名 | 大小 |

| COUNT_ASYNC_4SUB/ | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.asm.rpt | 7KB |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.done | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.fit.rpt | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.fit.smsg | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.fit.summary | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.flow.rpt | 7KB |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.map.rpt | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.map.summary | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.pin | |

| COUNT_ASYNC_4SUB/EX_ASYN_4SUB.pof | |

| ... | |

最新上传

-

zhengdai 打赏1000.00元 3天前

资料:STM32IAP使用说明

-

gsy幸运 打赏955.00元 3天前

资料:STM32IAP使用说明

-

小猫做电路 打赏855.00元 3天前

资料:STM32IAP使用说明

-

21ic小能手 打赏310.00元 3天前

用户:zhengdai

-

21ic小能手 打赏320.00元 3天前

用户:liqiang9090

-

21ic小能手 打赏310.00元 3天前

用户:gsy幸运

-

21ic小能手 打赏270.00元 3天前

用户:jh03551

-

21ic小能手 打赏240.00元 3天前

用户:小猫做电路

-

21ic小能手 打赏210.00元 3天前

用户:w178191520

-

21ic小能手 打赏90.00元 3天前

用户:kkfjenui

-

21ic小能手 打赏60.00元 3天前

用户:liao6

-

21ic小能手 打赏60.00元 3天前

用户:w1966891335

-

21ic小能手 打赏90.00元 3天前

用户:jh0355

-

21ic小能手 打赏30.00元 3天前

用户:xuzhen1

-

21ic小能手 打赏30.00元 3天前

用户:sun2152

-

21ic小能手 打赏50.00元 3天前

用户:xzxbybd

-

21ic小能手 打赏50.00元 3天前

用户:mulanhk

-

21ic小能手 打赏20.00元 3天前

用户:x15580286248

-

21ic小能手 打赏15.00元 3天前

用户:w993263495

-

21ic小能手 打赏30.00元 3天前

用户:玉落彼岸

-

21ic小能手 打赏20.00元 3天前

用户:铁蛋锅

-

21ic小能手 打赏10.00元 3天前

用户:zmcch

-

21ic小能手 打赏10.00元 3天前

-

21ic下载 打赏1.00元 3天前

用户:zzcyolo

-

21ic下载 打赏1.00元 3天前

用户:玉落彼岸

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

sdqdjqk 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

wisdomlin 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

799902619 打赏1.00元 3天前

资料:新立新龙软件

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

全部评论(1)

2020-03-15 17:21:42必过源码

好评