- 1

- 2

- 3

- 4

- 5

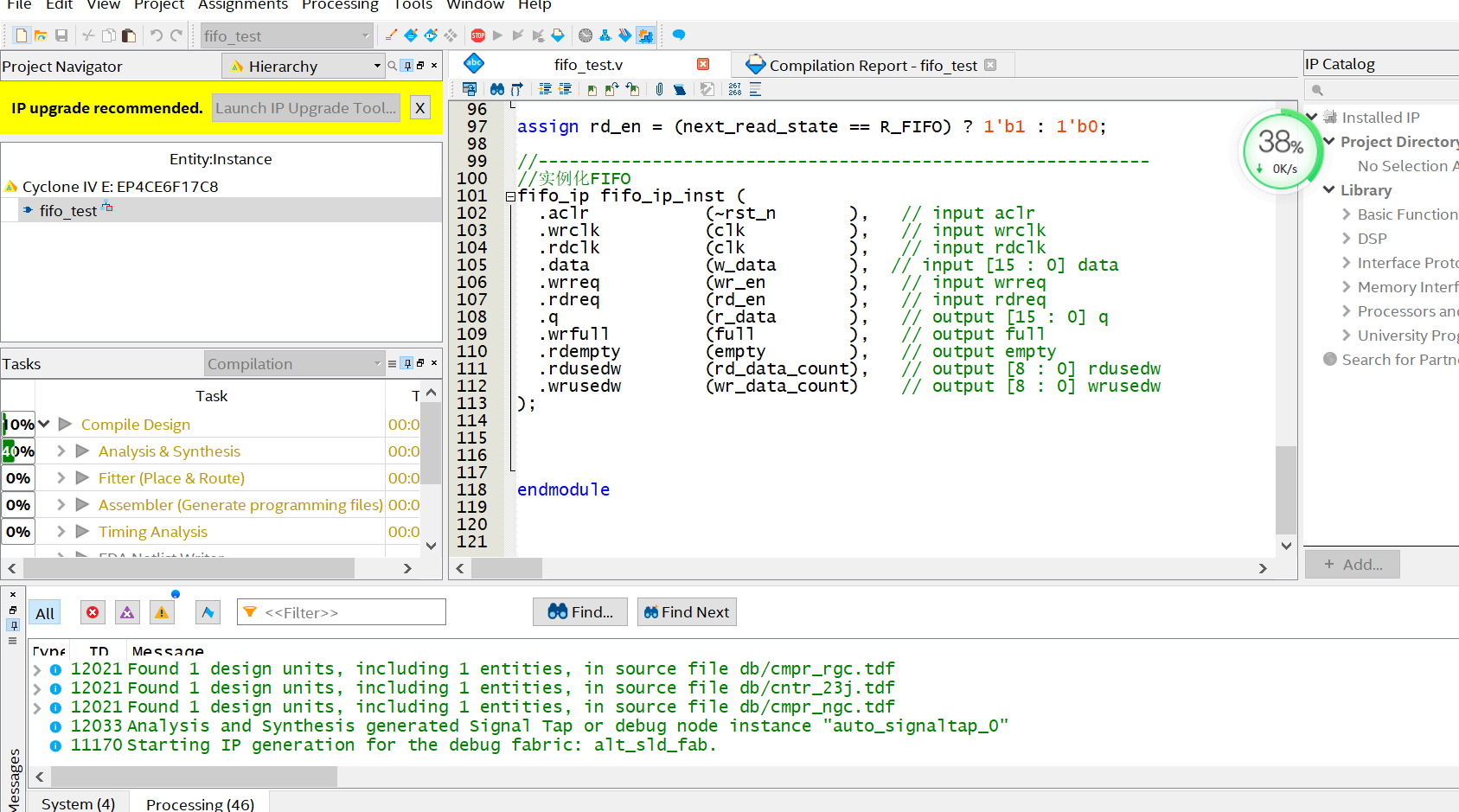

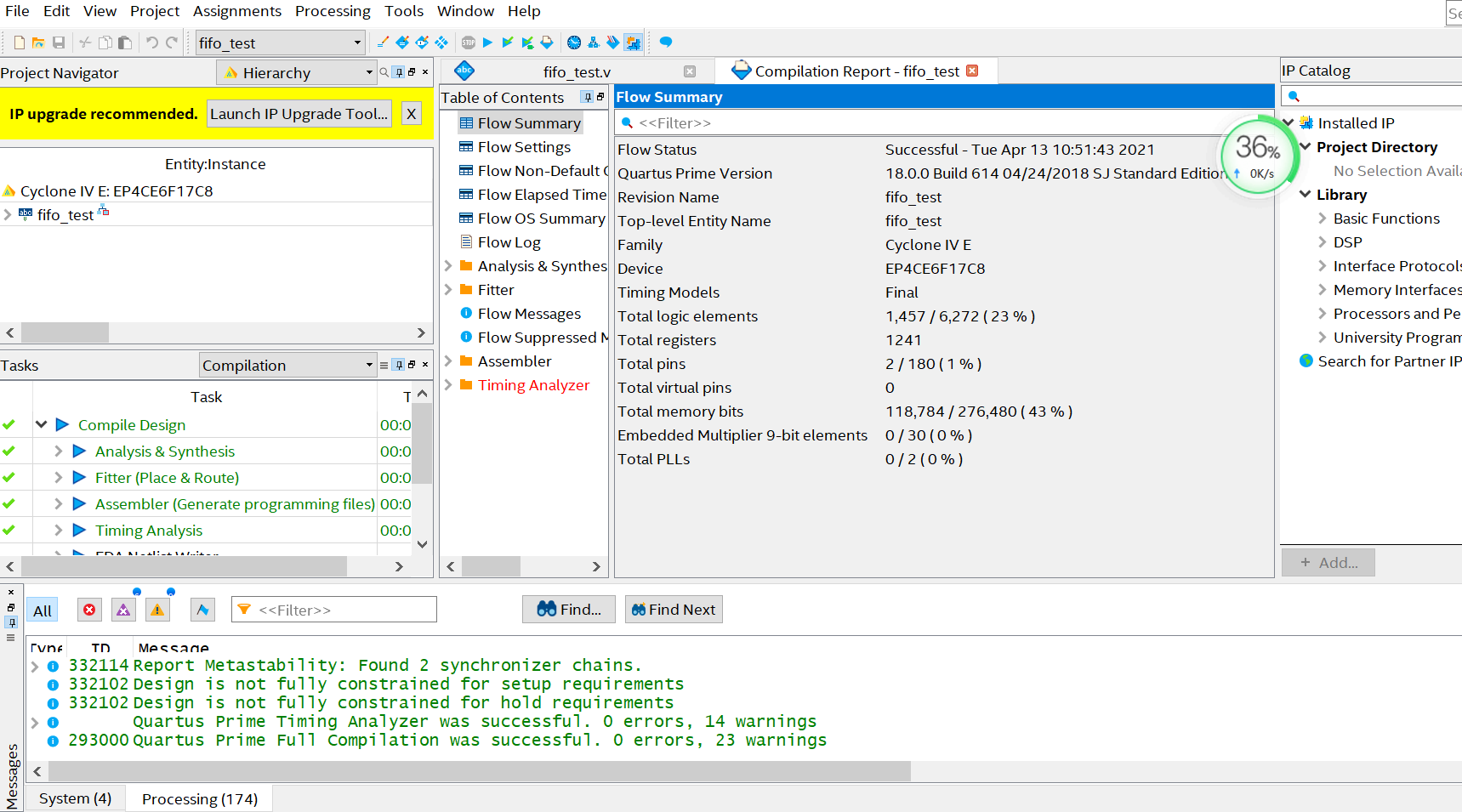

FPGA片内FIFO读写测试Verilog逻辑源码Quartus工程文件+文档说明 使用 FPGA

资料介绍

FPGA片内FIFO读写测试Verilog逻辑源码Quartus工程文件+文档说明,使用 FPGA 内部的 FIFO 以及程序对该 FIFO 的数据读写操作。FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

module fifo_test(

input clk, //50MHz时钟

input rst_n //复位信号,低电平有效

);

//-----------------------------------------------------------

localparam W_IDLE = 1;

localparam W_FIFO = 2;

localparam R_IDLE = 1;

localparam R_FIFO = 2;

reg[2:0] write_state;

reg[2:0] next_write_state;

reg[2:0] read_state;

reg[2:0] next_read_state;

reg[15:0] w_data; //FIFO写数据

wire wr_en; //FIFO写使能

wire rd_en; //FIFO读使能

wire[15:0] r_data; //FIFO读数据

wire full; //FIFO满信号

wire empty; //FIFO空信号

wire[8:0] rd_data_count;

wire[8:0] wr_data_count;

///产生FIFO写入的数据

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

write_state <= W_IDLE;

else

write_state <= next_write_state;

end

always@(*)

begin

case(write_state)

W_IDLE:

if(empty == 1'b1) //FIFO空, 开始写FIFO

next_write_state <= W_FIFO;

else

next_write_state <= W_IDLE;

W_FIFO:

if(full == 1'b1) //FIFO满

next_write_state <= W_IDLE;

else

next_write_state <= W_FIFO;

default:

next_write_state <= W_IDLE;

endcase

end

assign wr_en = (next_write_state == W_FIFO) ? 1'b1 : 1'b0;

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

w_data <= 16'd0;

else

if (wr_en == 1'b1)

w_data <= w_data + 1'b1;

else

w_data <= 16'd0;

end

///产生FIFO读的数据

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

read_state <= R_IDLE;

else

read_state <= next_read_state;

end

always@(*)

begin

case(read_state)

R_IDLE:

if(full == 1'b1) //FIFO满, 开始读FIFO

next_read_state <= R_FIFO;

else

next_read_state <= R_IDLE;

R_FIFO:

if(empty == 1'b1)

部分文件列表

| 文件名 | 大小 |

| 13.FPGA片内FIFO读写测试.pdf | |

| 13_fifo_test/ | |

| 13_fifo_test/db/ | |

| 13_fifo_test/db/.cmp.kpt | |

| 13_fifo_test/db/a_gray2bin_6ib.tdf | 2KB |

| 13_fifo_test/db/a_graycounter_1lc.tdf | 4KB |

| 13_fifo_test/db/a_graycounter_3p6.tdf | 4KB |

| 13_fifo_test/db/a_graycounter_577.tdf | 4KB |

| 13_fifo_test/db/a_graycounter_v6c.tdf | 4KB |

| 13_fifo_test/db/alt_synch_pipe_8pl.tdf | 3KB |

| 13_fifo_test/db/alt_synch_pipe_9pl.tdf | 3KB |

| ... | |

最新上传

-

21ic下载 打赏310.00元 5小时前

用户:zhengdai

-

21ic下载 打赏310.00元 5小时前

用户:liqiang9090

-

21ic下载 打赏330.00元 5小时前

用户:jh0355

-

21ic下载 打赏210.00元 5小时前

用户:小猫做电路

-

21ic下载 打赏240.00元 5小时前

用户:jh03551

-

21ic下载 打赏210.00元 5小时前

用户:gsy幸运

-

21ic下载 打赏70.00元 5小时前

用户:w178191520

-

21ic下载 打赏60.00元 5小时前

用户:sun2152

-

21ic下载 打赏80.00元 5小时前

用户:江岚

-

21ic下载 打赏60.00元 5小时前

用户:xuzhen1

-

21ic下载 打赏20.00元 5小时前

用户:kk1957135547

-

21ic下载 打赏40.00元 5小时前

用户:潇潇江南

-

21ic下载 打赏20.00元 5小时前

用户:w993263495

-

21ic下载 打赏20.00元 5小时前

用户:w1966891335

-

21ic下载 打赏70.00元 5小时前

用户:有理想666

-

21ic下载 打赏35.00元 5小时前

用户:xzxbybd

-

21ic下载 打赏15.00元 5小时前

用户:x15580286248

-

21ic下载 打赏25.00元 5小时前

用户:铁蛋锅

-

21ic下载 打赏35.00元 5小时前

用户:mulanhk

-

21ic下载 打赏25.00元 5小时前

用户:曲鹏

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

全部评论(0)