- 1

- 2

- 3

- 4

- 5

epm240开发板Verilog例程按键消抖实验工程文件源码+说明文档

资料介绍

epm240开发板Verilog例程按键消抖实验工程文件源码+说明文档

键盘分编码键盘和非编码键盘。键盘上闭合键的识别由专用的硬件编码器实现,并产生

键编码号或键值的称为编码键盘,如计算机键盘。而靠软件编程来识别的称为非编码键盘。

在一般嵌入式应用中,用的最多的是非编码键盘,也有用到编码键盘的。非编码键盘有分为:

独立键盘和行列式(又称为矩阵式)键盘。

如图5.3 所示,按键在闭合和断开时,触点会存在抖动现象。在按键按下或者是释放的

时候都会出现一个不稳定的抖动时间,如果不处理好这个抖动时间,我们就无法处理好按键

编码,所以我们的设计中必须有效消除按键抖动。

module sw_debounce(

clk,rst_n,

sw1_n,sw2_n,sw3_n,

led_d1,led_d2,led_d3

);

input clk; //主时钟信号,50MHz

input rst_n; //复位信号,低有效

input sw1_n,sw2_n,sw3_n; //三个独立按键,低表示按下

output led_d1,led_d2,led_d3; //发光二极管,分别由按键控制

//---------------------------------------------------------------------------

reg[2:0] key_rst;

always @(posedge clk or negedge rst_n)

if (!rst_n) key_rst <= 3'b111;

else key_rst <= {sw3_n,sw2_n,sw1_n};

reg[2:0] key_rst_r; //每个时钟周期的上升沿将low_sw 信号锁存到low_sw_r 中

always @ ( posedge clk or negedge rst_n )

if (!rst_n) key_rst_r <= 3'b111;

else key_rst_r <= key_rst;

//当寄存器key_rst 由1 变为0 时,led_an 的值变为高,维持一个时钟周期

wire[2:0] key_an = key_rst_r & ( ~key_rst);

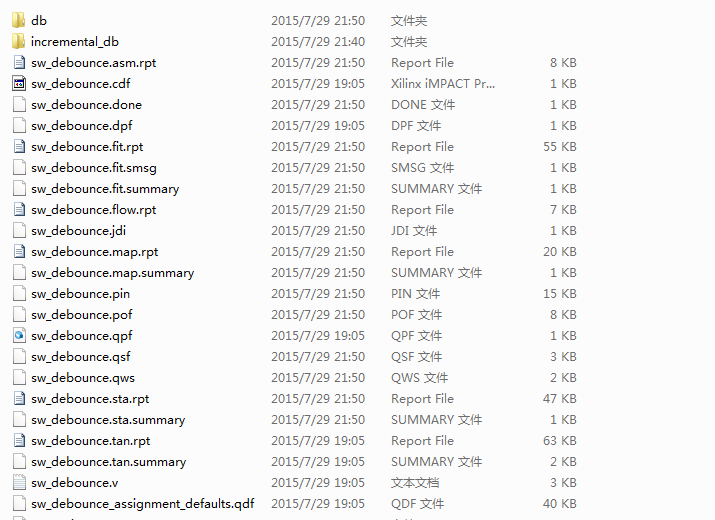

部分文件列表

| 文件名 | 大小 |

| keyscanverilog/ | |

| keyscanverilog/db/ | |

| keyscanverilog/db/.cmp.kpt | |

| keyscanverilog/db/logic_util_heursitic.dat | 2KB |

| keyscanverilog/db/prev_cmp_sw_debounce.asm.qmsg | 2KB |

| keyscanverilog/db/prev_cmp_sw_debounce.fit.qmsg | |

| keyscanverilog/db/prev_cmp_sw_debounce.map.qmsg | 4KB |

| keyscanverilog/db/prev_cmp_sw_debounce.qmsg | |

| keyscanverilog/db/prev_cmp_sw_debounce.tan.qmsg | |

| keyscanverilog/db/sw_debounce.(0).cnf.cdb | 3KB |

| keyscanverilog/db/sw_debounce.(0).cnf.hdb | 1KB |

| ... | |

最新上传

-

21ic小能手 打赏5.00元 1天前

-

21下载积分 打赏1.00元 1天前

用户:德才兼备

-

mulanhk 打赏1.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏3.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

资料:数控电子负载-CH552

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:zhengdai

-

21ic下载 打赏310.00元 3天前

用户:liqiang9090

-

21ic下载 打赏330.00元 3天前

用户:jh0355

-

21ic下载 打赏210.00元 3天前

用户:小猫做电路

-

21ic下载 打赏240.00元 3天前

用户:jh03551

-

21ic下载 打赏210.00元 3天前

用户:gsy幸运

-

21ic下载 打赏70.00元 3天前

用户:w178191520

-

21ic下载 打赏60.00元 3天前

用户:sun2152

-

21ic下载 打赏80.00元 3天前

用户:江岚

-

21ic下载 打赏60.00元 3天前

用户:xuzhen1

-

21ic下载 打赏20.00元 3天前

用户:kk1957135547

-

21ic下载 打赏40.00元 3天前

用户:潇潇江南

-

21ic下载 打赏20.00元 3天前

用户:w993263495

-

21ic下载 打赏20.00元 3天前

用户:w1966891335

-

21ic下载 打赏70.00元 3天前

用户:有理想666

-

21ic下载 打赏35.00元 3天前

用户:xzxbybd

-

21ic下载 打赏15.00元 3天前

用户:x15580286248

-

21ic下载 打赏25.00元 3天前

用户:铁蛋锅

-

21ic下载 打赏35.00元 3天前

用户:mulanhk

全部评论(0)