- 1

- 2

- 3

- 4

- 5

Cyclone2 FPGA读写 ADC_TLC549实验Verilog逻辑源码Quartus工程文件

资料介绍

Cyclone2 FPGA读写 ADC_TLC549实验Verilog逻辑源码Quartus工程文件

module AD_TLC549 (

//input

input sys_clk , //system clock;

input sys_rst_n , //system reset, low is active;

input AD_IO_DATA ,

//output

output reg AD_IO_CLK ,

output reg AD_CS ,

output reg [7:0] LED

);

//Reg define

reg [6:0] div_cnt ;

reg ad_clk ;

reg [4:0] ctrl_cnt ;

reg [7:0] ad_data_shift ;

//Wire define

//************************************************************************************

//** Main Program

//**

//************************************************************************************

// counter used for div osc clk to ad ctrl clk 50M/64 = 0.78Mhz

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

div_cnt <= 6'b0;

else

div_cnt <= div_cnt + 6'b1;

end

//gen ad_clk

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

ad_clk <= 1'b0 ;

else if ( div_cnt <= 6'd31 )

ad_clk <= 1'b1 ;

else

ad_clk <= 1'b0 ;

end

// ad ctrl signal gen

// ctrl_cnt 0 - 32is for ad ctrl

always @(posedge ad_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

ctrl_cnt <= 5'b0;

else

ctrl_cnt <= ctrl_cnt + 5'b1;

end

always @(posedge ad_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

AD_IO_CLK <= 1'b0;

else if ( ctrl_cnt == 5'd6 || ctrl_cnt == 5'd8 || ctrl_cnt == 5'd10

|| ctrl_cnt == 5'd12 || ctrl_cnt == 5'd14 || ctrl_cnt == 5'd16

|| ctrl_cnt == 5'd18 || ctrl_cnt == 5'd20 ) // ad clk low

AD_IO_CLK <= 1'b1;

else

AD_IO_CLK <= 1'b0;

end

always @(posedge ad_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

AD_CS <= 1'b1;

else if ( ctrl_cnt >= 5'd1 && ctrl_cnt <= 5'd25 ) // ad output cs

AD_CS <= 1'b0;

else

AD_CS <= 1'b1;

end

// shift AD return analog DATA to ad_data_shift reg use AD_IO_CLK rising edge

always @(posedge ad_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

ad_data_shift <= 8'b0;

else if ( AD_CS == 1'b1 )

ad_data_shift <= 8'b0;

else if ( AD_IO_CLK == 1'b1 )

ad_data_shift <= { ad_data_shift[6:0], AD_IO_DATA } ;

else ;

end

//display AD sample data to LED when ad_data_shift is constanct

always @(posedge ad_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0)

LED <= 8'b0

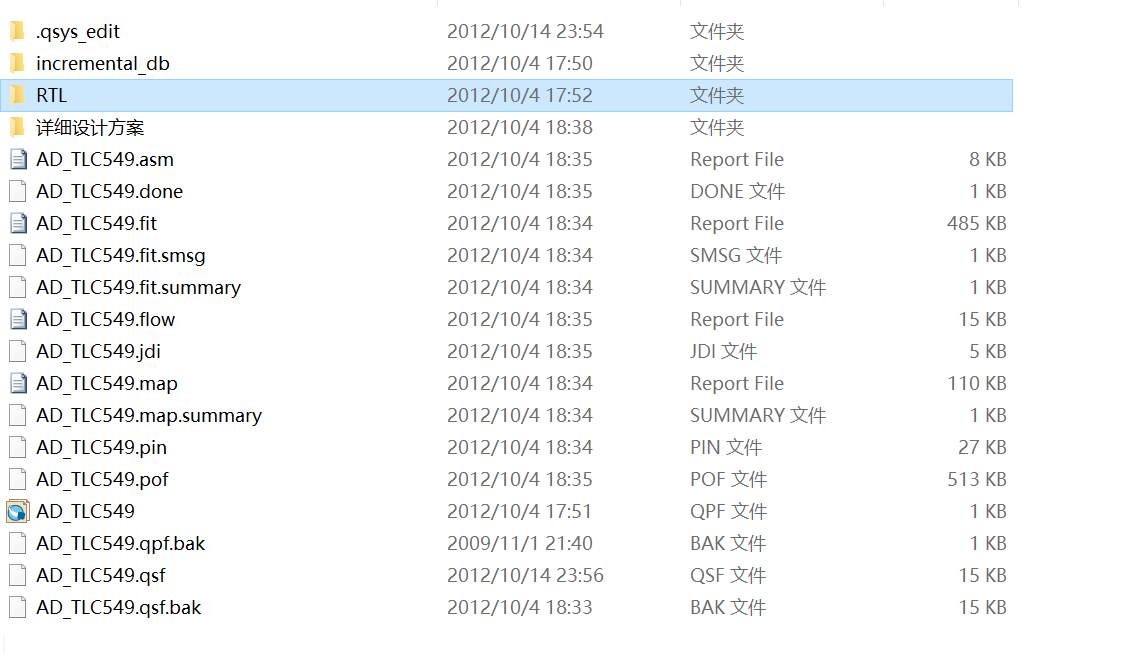

部分文件列表

| 文件名 | 大小 |

| AD_TLC549/ | |

| AD_TLC549/.qsys_edit/ | |

| AD_TLC549/.qsys_edit/filters.xml | |

| AD_TLC549/.qsys_edit/preferences.xml | |

| AD_TLC549/AD_TLC549.asm.rpt | 8KB |

| AD_TLC549/AD_TLC549.done | |

| AD_TLC549/AD_TLC549.fit.rpt | |

| AD_TLC549/AD_TLC549.fit.smsg | 1KB |

| AD_TLC549/AD_TLC549.fit.summary | 1KB |

| AD_TLC549/AD_TLC549.flow.rpt | |

| AD_TLC549/AD_TLC549.jdi | 4KB |

| ... | |

最新上传

-

21ic小能手 打赏5.00元 2天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏310.00元 3天前

用户:gsy幸运

-

21ic下载 打赏310.00元 3天前

用户:小猫做电路

-

21ic下载 打赏360.00元 3天前

用户:mulanhk

-

21ic下载 打赏230.00元 3天前

用户:江岚

-

21ic下载 打赏230.00元 3天前

用户:潇潇江南

-

21ic下载 打赏210.00元 3天前

用户:zhengdai

-

21ic下载 打赏160.00元 3天前

用户:lanmukk

-

21ic下载 打赏130.00元 3天前

用户:jh03551

-

21ic下载 打赏110.00元 3天前

用户:liqiang9090

-

21ic下载 打赏110.00元 3天前

用户:jh0355

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic下载 打赏20.00元 3天前

用户:w178191520

-

21ic下载 打赏30.00元 3天前

用户:sun2152

-

21ic下载 打赏30.00元 3天前

用户:xuzhen1

-

21ic下载 打赏20.00元 3天前

用户:w993263495

-

21ic下载 打赏15.00元 3天前

用户:kk1957135547

-

21ic下载 打赏15.00元 3天前

用户:eaglexiong

-

21ic下载 打赏15.00元 3天前

用户:w1966891335

-

21ic下载 打赏25.00元 3天前

用户:烟雨

-

21ic下载 打赏75.00元 3天前

用户:有理想666

-

21ic下载 打赏10.00元 3天前

用户:x15580286248

-

21ic下载 打赏40.00元 3天前

用户:xzxbybd

-

21ic下载 打赏10.00元 3天前

-

21ic下载 打赏10.00元 3天前

用户:sfgplj123

-

21ic下载 打赏10.00元 3天前

用户:dadengpao

-

21ic小能手 打赏10.00元 3天前

资料:自己编写的CRC校验工具

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

shenzhenliugang 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏10.00元 3天前

-

21ic小能手 打赏5.00元 3天前

-

21ic小能手 打赏5.00元 3天前

全部评论(0)