推荐星级:

- 1

- 2

- 3

- 4

- 5

FPGA中PLL模块的测试代码,代码通过例化一个PLL将25MHz系统时钟倍频到50MHz

资料介绍

FPGA中PLL模块的测试代码,代码通过例化一个PLL将25MHz系统时钟倍频到50MHz,然后通过两个不同频率时钟控制两个LED灯闪烁,通过闪烁频率可用观察PLL倍频效果.rar

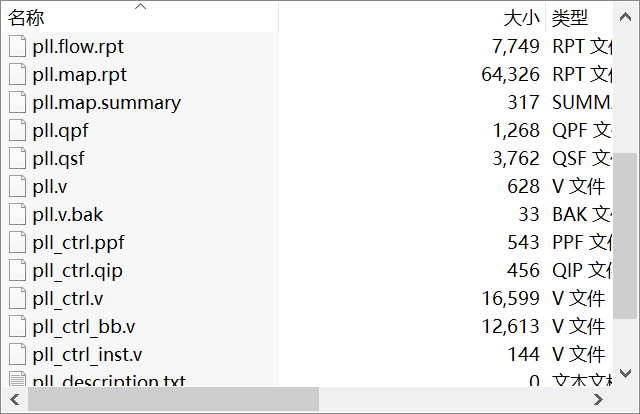

部分文件列表

| 文件名 | 文件大小 | 修改时间 |

| Pll_prj/.sopc_builder/filters.xml | 1KB | 2012-04-27 12:47:56 |

| Pll_prj/db/logic_util_heursitic.dat | 1KB | 2012-04-27 12:27:06 |

| Pll_prj/db/pll.(0).cnf.cdb | 1KB | 2012-04-27 12:01:42 |

| Pll_prj/db/pll.(0).cnf.hdb | 1KB | 2012-04-27 12:01:42 |

| Pll_prj/db/pll.(1).cnf.cdb | 2KB | 2012-04-27 12:01:42 |

| Pll_prj/db/pll.(1).cnf.hdb | 1KB | 2012-04-27 12:01:42 |

| Pll_prj/db/pll.(2).cnf.cdb | 2KB | 2012-04-27 12:01:42 |

| Pll_prj/db/pll.(2).cnf.hdb | 1KB | 2012-04-27 12:01:42 |

| Pll_prj/db/pll.cbx.xml | 1KB | 2012-04-27 12:27:06 |

| Pll_prj/db/pll.cmp.rdb | 8KB | 2012-04-27 12:27:06 |

| Pll_prj/db/pll.cmp_merge.kpt | 1KB | 2012-04-27 12:27:06 |

| ... | ||

全部评论(0)